主题中讨论的其他器件:HALCOGEN

您好!

是否可以将 mibSPI 用作标准 SPI? 如果是,您是否有代码示例?

此致、

Cosmin Briceag

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Cosmin、

是的、这是可能的。 MibSPI 将运行在两种模式兼容性和多缓冲模式下、在兼容模式下、MibSPI 的运行方式与 SPI 完全一样

您能不能浏览下面的主题

(+) CCS/TMS570LC4357:兼容模式下的 SPI 回送不起作用-基于 Arm 的微控制器论坛-基于 Arm 的微控制器- TI E2E 支持论坛

随附了用于 LC4357的代码、您可以将其作为参考、也可以在 HALCoGen 中应用相同的配置并尝试。

或其他

您也可以尝试使用以下链接

如果您在参考上述链接后仍面临困惑、我可以为您提供 RM48x 的示例代码。

--

谢谢、此致、

Jagadish。

您好 Jagadish、

很抱歉耽误你的回答。 嗯、我设法使它仅适用于 SPI3。 虽然 SPI1具有相同的配置、但不会生成时钟。 另一个奇怪的现象是、逻辑分析仪在不生成时钟的情况下记录 MOSI/ MISO 活动。 我对 SPI3使用了相同的逻辑分析仪、那里的一切都很好。 我使用自己的 CS。

我对 SPI1有什么特别的事吗?

/** bring SPI out of reset */

spiREG1->GCR0 = 0U;

spiREG1->GCR0 = 1U;

/** SPI1 master mode and clock configuration */

spiREG1->GCR1 = (spiREG1->GCR1 & 0xFFFFFFFCU) | ((uint32)((uint32)1U << 1U) /* CLOKMOD */

| 1U); /* MASTER */

/** SPI1 enable pin configuration */

spiREG1->INT0 = (spiREG1->INT0 & 0xFEFFFFFFU)| (uint32)((uint32)0U << 24U); /* ENABLE HIGHZ */

/** - Delays */

spiREG1->DELAY = (uint32)((uint32)0U << 24U) /* C2TDELAY */

| (uint32)((uint32)0U << 16U) /* T2CDELAY */

| (uint32)((uint32)0U << 8U) /* T2EDELAY */

| (uint32)((uint32)0U << 0U); /* C2EDELAY */

/** - Data Format 0 */

spiREG1->FMT0 = (uint32)((uint32)0U << 24U) /* wdelay */

| (uint32)((uint32)0U << 23U) /* parity Polarity */

| (uint32)((uint32)0U << 22U) /* parity enable */

| (uint32)((uint32)0U << 21U) /* wait on enable */

| (uint32)((uint32)0U << 20U) /* shift direction */

| (uint32)((uint32)0U << 17U) /* clock polarity */

| (uint32)((uint32)0U << 16U) /* clock phase */

| (uint32)((uint32)21U << 8U) /* baudrate prescale */

| (uint32)((uint32)8U << 0U); /* data word length */

/** - Data Format 1 */

spiREG1->FMT1 = (uint32)((uint32)0U << 24U) /* wdelay */

| (uint32)((uint32)0U << 23U) /* parity Polarity */

| (uint32)((uint32)0U << 22U) /* parity enable */

| (uint32)((uint32)0U << 21U) /* wait on enable */

| (uint32)((uint32)0U << 20U) /* shift direction */

| (uint32)((uint32)0U << 17U) /* clock polarity */

| (uint32)((uint32)0U << 16U) /* clock phase */

| (uint32)((uint32)109U << 8U) /* baudrate prescale */

| (uint32)((uint32)16U << 0U); /* data word length */

/** - Data Format 2 */

spiREG1->FMT2 = (uint32)((uint32)0U << 24U) /* wdelay */

| (uint32)((uint32)0U << 23U) /* parity Polarity */

| (uint32)((uint32)0U << 22U) /* parity enable */

| (uint32)((uint32)0U << 21U) /* wait on enable */

| (uint32)((uint32)0U << 20U) /* shift direction */

| (uint32)((uint32)0U << 17U) /* clock polarity */

| (uint32)((uint32)0U << 16U) /* clock phase */

| (uint32)((uint32)109U << 8U) /* baudrate prescale */

| (uint32)((uint32)16U << 0U); /* data word length */

/** - Data Format 3 */

spiREG1->FMT3 = (uint32)((uint32)0U << 24U) /* wdelay */

| (uint32)((uint32)0U << 23U) /* parity Polarity */

| (uint32)((uint32)0U << 22U) /* parity enable */

| (uint32)((uint32)0U << 21U) /* wait on enable */

| (uint32)((uint32)0U << 20U) /* shift direction */

| (uint32)((uint32)0U << 17U) /* clock polarity */

| (uint32)((uint32)0U << 16U) /* clock phase */

| (uint32)((uint32)109U << 8U) /* baudrate prescale */

| (uint32)((uint32)16U << 0U); /* data word length */

/** - set interrupt levels */

spiREG1->LVL = (uint32)((uint32)0U << 9U) /* TXINT */

| (uint32)((uint32)0U << 8U) /* RXINT */

| (uint32)((uint32)0U << 6U) /* OVRNINT */

| (uint32)((uint32)0U << 4U) /* BITERR */

| (uint32)((uint32)0U << 3U) /* DESYNC */

| (uint32)((uint32)0U << 2U) /* PARERR */

| (uint32)((uint32)0U << 1U) /* TIMEOUT */

| (uint32)((uint32)0U << 0U); /* DLENERR */

/** - clear any pending interrupts */

spiREG1->FLG |= 0xFFFFU;

/** - enable interrupts */

spiREG1->INT0 = (spiREG1->INT0 & 0xFFFF0000U)

| (uint32)((uint32)0U << 9U) /* TXINT */

| (uint32)((uint32)0U << 8U) /* RXINT */

| (uint32)((uint32)0U << 6U) /* OVRNINT */

| (uint32)((uint32)0U << 4U) /* BITERR */

| (uint32)((uint32)0U << 3U) /* DESYNC */

| (uint32)((uint32)0U << 2U) /* PARERR */

| (uint32)((uint32)0U << 1U) /* TIMEOUT */

| (uint32)((uint32)0U << 0U); /* DLENERR */

/** @b initialize @b SPI1 @b Port */

/** - SPI1 Port output values */

spiREG1->PC3 = (uint32)((uint32)1U << 0U) /* SCS[0] */

| (uint32)((uint32)1U << 1U) /* SCS[1] */

| (uint32)((uint32)1U << 2U) /* SCS[2] */

| (uint32)((uint32)1U << 3U) /* SCS[3] */

| (uint32)((uint32)1U << 4U) /* SCS[4] */

| (uint32)((uint32)1U << 5U) /* SCS[5] */

| (uint32)((uint32)0U << 8U) /* ENA */

| (uint32)((uint32)0U << 9U) /* CLK */

| (uint32)((uint32)0U << 10U) /* SIMO[0] */

| (uint32)((uint32)0U << 11U) /* SOMI[0] */

| (uint32)((uint32)0U << 17U) /* SIMO[1] */

| (uint32)((uint32)0U << 25U); /* SOMI[1] */

/** - SPI1 Port direction */

spiREG1->PC1 = (uint32)((uint32)0U << 0U) /* SCS[0] */

| (uint32)((uint32)0U << 1U) /* SCS[1] */

| (uint32)((uint32)0U << 2U) /* SCS[2] */

| (uint32)((uint32)0U << 3U) /* SCS[3] */

| (uint32)((uint32)0U << 4U) /* SCS[4] */

| (uint32)((uint32)0U << 5U) /* SCS[5] */

| (uint32)((uint32)0U << 8U) /* ENA */

| (uint32)((uint32)1U << 9U) /* CLK */

| (uint32)((uint32)1U << 10U) /* SIMO[0] */

| (uint32)((uint32)0U << 11U) /* SOMI[0] */

| (uint32)((uint32)0U << 17U) /* SIMO[1] */

| (uint32)((uint32)0U << 25U); /* SOMI[1] */

/** - SPI1 Port open drain enable */

spiREG1->PC6 = (uint32)((uint32)0U << 0U) /* SCS[0] */

| (uint32)((uint32)0U << 1U) /* SCS[1] */

| (uint32)((uint32)0U << 2U) /* SCS[2] */

| (uint32)((uint32)0U << 3U) /* SCS[3] */

| (uint32)((uint32)0U << 4U) /* SCS[4] */

| (uint32)((uint32)0U << 5U) /* SCS[5] */

| (uint32)((uint32)0U << 8U) /* ENA */

| (uint32)((uint32)0U << 9U) /* CLK */

| (uint32)((uint32)0U << 10U) /* SIMO[0] */

| (uint32)((uint32)0U << 11U) /* SOMI[0] */

| (uint32)((uint32)0U << 17U) /* SIMO[1] */

| (uint32)((uint32)0U << 25U); /* SOMI[1] */

/** - SPI1 Port pullup / pulldown selection */

spiREG1->PC8 = (uint32)((uint32)1U << 0U) /* SCS[0] */

| (uint32)((uint32)1U << 1U) /* SCS[1] */

| (uint32)((uint32)1U << 2U) /* SCS[2] */

| (uint32)((uint32)1U << 3U) /* SCS[3] */

| (uint32)((uint32)1U << 4U) /* SCS[4] */

| (uint32)((uint32)1U << 5U) /* SCS[5] */

| (uint32)((uint32)1U << 8U) /* ENA */

| (uint32)((uint32)1U << 9U) /* CLK */

| (uint32)((uint32)1U << 10U) /* SIMO[0] */

| (uint32)((uint32)1U << 11U) /* SOMI[0] */

| (uint32)((uint32)1U << 17U) /* SIMO[1] */

| (uint32)((uint32)1U << 25U); /* SOMI[1] */

/** - SPI1 Port pullup / pulldown enable*/

spiREG1->PC7 = (uint32)((uint32)1U << 0U) /* SCS[0] */

| (uint32)((uint32)0U << 1U) /* SCS[1] */

| (uint32)((uint32)0U << 2U) /* SCS[2] */

| (uint32)((uint32)1U << 3U) /* SCS[3] */

| (uint32)((uint32)1U << 4U) /* SCS[4] */

| (uint32)((uint32)1U << 5U) /* SCS[5] */

| (uint32)((uint32)1U << 8U) /* ENA */

| (uint32)((uint32)0U << 9U) /* CLK */

| (uint32)((uint32)0U << 10U) /* SIMO[0] */

| (uint32)((uint32)1U << 11U) /* SOMI[0] */

| (uint32)((uint32)1U << 17U) /* SIMO[1] */

| (uint32)((uint32)1U << 25U); /* SOMI[1] */

/* SPI1 set all pins to functional */

spiREG1->PC0 = (uint32)((uint32)0U << 0U) /* SCS[0] */

| (uint32)((uint32)0U << 1U) /* SCS[1] */

| (uint32)((uint32)0U << 2U) /* SCS[2] */

| (uint32)((uint32)0U << 3U) /* SCS[3] */

| (uint32)((uint32)0U << 4U) /* SCS[4] */

| (uint32)((uint32)0U << 5U) /* SCS[5] */

| (uint32)((uint32)0U << 8U) /* ENA */

| (uint32)((uint32)1U << 9U) /* CLK */

| (uint32)((uint32)1U << 10U) /* SIMO[0] */

| (uint32)((uint32)1U << 11U) /* SOMI[0] */

| (uint32)((uint32)0U << 17U) /* SIMO[1] */

| (uint32)((uint32)0U << 25U); /* SOMI[1] */

/** - Initialize TX and RX data buffer Status */

g_spiPacket_t[0U].tx_data_status = SPI_READY;

g_spiPacket_t[0U].rx_data_status = SPI_READY;

/** - Finally start SPI1 */

spiREG1->GCR1 = (spiREG1->GCR1 & 0xFEFFFFFFU) | 0x01000000U;您好、Cosmin、

我不知道您使用的是哪个板、以及您在 SPI1的哪些引脚上测量信号。

如果可能、请尝试附加整个项目、以便我可以验证您的引脚配置和初始化。

或者、请确保以下事项、

1.确保在引脚复用配置中启用 MibSPI1

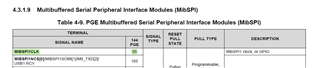

2.如果您使用 PGE 封装、则 MIBSPI1CLK 位于器件的第95个引脚上、因此请确保在板上粘贴正确的引脚

--

谢谢、此致、

Jagadish。