您好!

我正在从事一个涉及两个13位编码器的项目。 因此、我很有效率地使用内置接口。 问题是、位置是浮动的。 我有一个提供 A 和 B 信号的伺服控制器(它也可以是单端和微分信号)

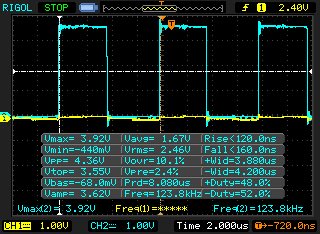

以下是信号:

我是否可以通过任何方法来提高 QEI 采样率?

当前时钟:

// //将时钟设置为以50MHz 的频率从 PLL 运行 // ROM_SysCtlClockSet (SYSCTL_SYSDIV_4 | SYSCTL_USE_PLL | SYSCTL_OSC_MAIN | SYSCTL_XTAL_16MHz);

我是否应将其增加到80MHz?

我真的很不明白,我必须在下个星期五完成这项工作,因为它将是“欧洲研究人员之夜(夜晚)”,机器原型将被展示出来。 目前、我跟踪两个10圈的帖子、以跟踪伺服程序。 但是、由于它们具有内置的编码器、我愿意使用它。 (减少机械部件、其使用寿命将比电位计长。)

PCB 尚未最终确定、将在内部制造、因此添加硬件元件是一个选项。

请帮我解决-