主题中讨论的其他器件:UNIFLASH、

TI 按照数据表的首选做法推出的 TM4C129X 是令人感到受骗的。

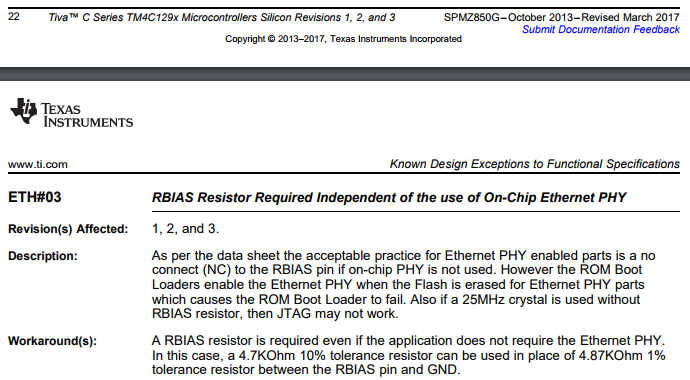

数据表的表31-7说明未使用的以太网 PHY 应保持 RBIAS 未连接。 这是首选做法。 这会使芯片成为砖型。

我从 CM 收到了未编程的 TM4C129X、但未将4.87k 电阻器连接到 RBIAS。 无法对微控制器进行编程。 CCS 给我错误2062。

Amit 声称错误是由微控制器内试图打开 PHY 的代码引起的。 但这些器件从未进行过编程。

我必须(1)卸下25MHz 晶体。 (2)错误代码中不开启 PHY 的闪存。 (3)重新焊接25MHz 晶振。 (4)做真正的工作。

我对浪费的时间感到相当沮丧。 我认为这一问题可能仍然存在、因为大多数客户在没有使用 PHY 的情况下不会购买此芯片。 我打算在最终设计中使用 PHY、但这个顺序是一个仅测试 EPI 和 LCD 接口的原型。