主题中讨论的其他器件:ADS1298、 ISO7840、 ISO7841、 TM4C1294NCPDT

你好!

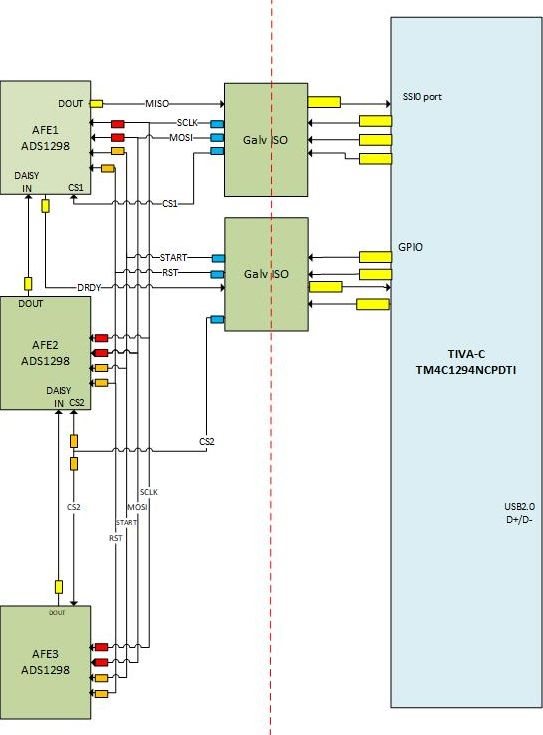

我们有一个将多个 ADS1298 (3个)连接到 TM4C1294的系统。

3个 ADS1298以菊花链方式连接在一起。(在初始化/工作期间、可以通过芯片选择 AFE1或 AFE2+AFE3)

在 SPI 线路(串行终端)的正确端接方面、我需要一些帮助、尤其是 SCLK 和 MOSI 线路(以防止振铃并最大限度地降低 EMI 辐射)

这是一个简化的方框图。

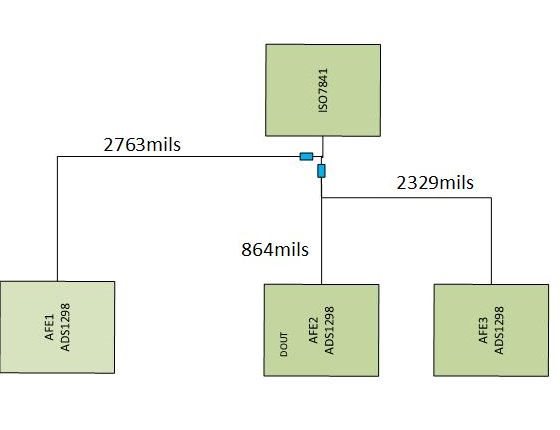

此时、我确信 黄色端接点位置良好。 但我不知道如何最好地端接 SCLK 和 MOSI 线路、因为在电隔离之后、线路被路由到3条线路上、并且3段的长度不同。 AFE2和 AFE3彼此靠近。

那么我的问题是在哪里放置端接电阻器?

我是否只需要在 SCLK 和 MOSI 的红色端接点放置、或者我是否还需要/仅需要在蓝色端接? 那么,要在每个腿上的 Y 分割之后,或者/和分割之前(也是)?

我对其他公共线路的启动、复位、CS 也有同样的问题、但由于这些线路在初始化后不会改变其状态、如果我只在蓝点放置端接、这些线路可能不会产生问题。

谢谢!

最好的 Regardss

Lou