主题中讨论的其他器件:REF2033、 TM4C1294KCPDT、 TM4C1294NCPDT

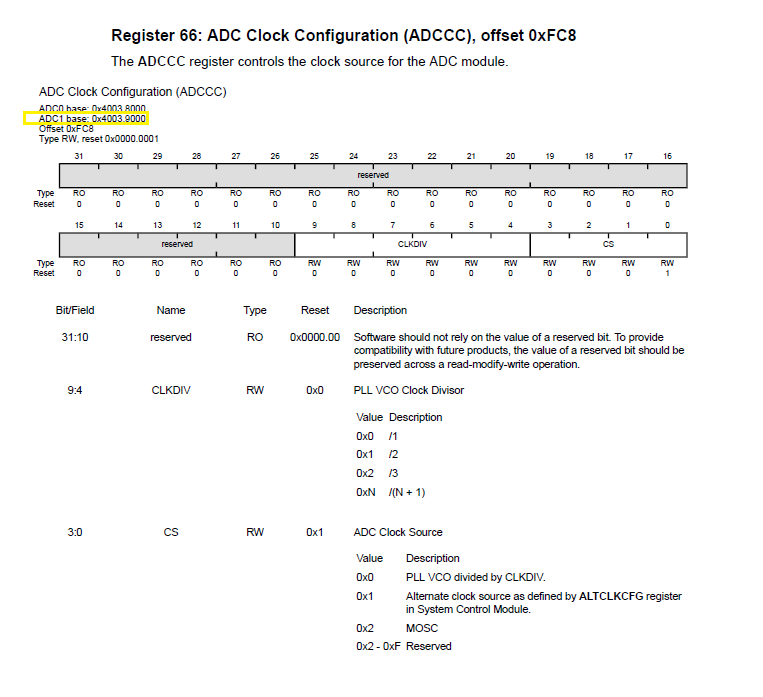

ADC1温度传感器读取和其他无法解释 的序列发生器行为的奇怪问题 可能 与时钟相关。 过去的数据表 15.3.2.7 状态 ADC0 通过 ADCCC REG66设置 ADC 模块的时钟。 在 通过 ADCClockConfigSet()配置 ADC 时钟时,大多数人都不会考虑检查 REG 66该语句的计数器。 ADC 模块包含 ADC0和 ADC1模块或外设。 如果 未配置 ADC1时钟分频值1、则默认 ADC1时钟分频值1在 PLL 速度下产生 ADCCLK、即 REG 66基址0x4003.9000实际有效。

当 只调用 ADCClockConfigSet() 来为 0x4003.8000 ADC 模块配置 ADCCC REG66时,显示 ADC1基址的寄存器66会使15.3.2.7语句变得奇数。 似乎存在一个拼写错误 、即 ADC0设置模块 时钟、大多数人 认为 这是指 两个 ADC 块。 最近发现 的 ADC1基地址 也存在 REG66并且 ADCClockConfigSet()只使用 ADC0基地址调用一次。

15.3.2.7模块时钟:系统时钟频率必须与 ADC 时钟相同或更高。 所有 ADC 模块共用同一个时钟源、以便在转换单元之间同步数据采样、其选择和编程由 ADC0的 ADCCC 寄存器提供。 ADC 模块不能以不同的转换速率运行。

ADC0和 ADC1模块是否共享 ADC 模块相同的时钟源 、或者是否为 REG-66中所示的实际独立配置的时钟源? 也许在 外设块的图中说明时钟源的另一个好理由!