主题中讨论的其他器件:LM94022、INA240

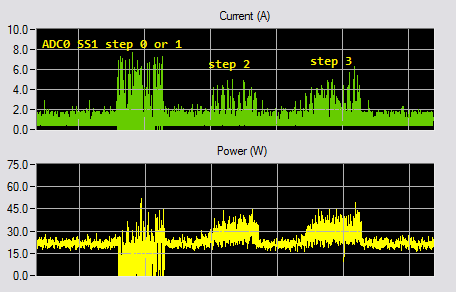

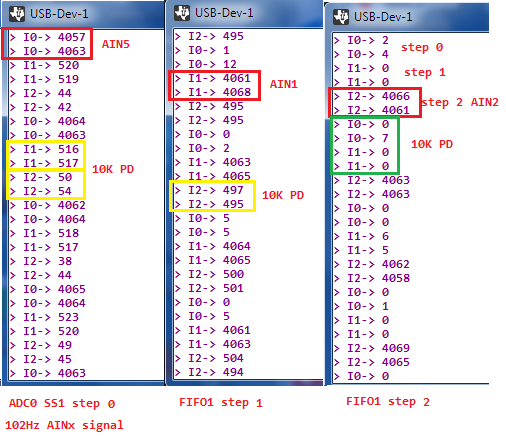

在对 ADC0 SS1步进0或1 FIFO1进行更多 kiss 测试后、数据似乎会在示波器小工具中产生差分信号。 但是、如果禁用了步骤0、步骤2或步骤3会产生如下所示的相同结果。 第1步的数字值读数 比 示波器小工具可以显示的值多得多。

如何 在通道对上设置输入差分模式、例如、当未 通过软件配置时、步骤0或1? 如果 FIFO 被预触发以呈现下一个步骤的结果、那么在代码中、步骤0或1的相同差分输出结果。 在 AIN5、AIN2、AIN1上、同一信号中是否不存在差分信号? 这使我疯了、因为它不会增加匹配通道 Rs 阻抗的典型行为。 什么会导致 AIN 通道允许输入 信号低于其他通道? 这一问题似乎也会导致 VREFN 饱和无约束。

//MAP_ADCSequenceStepConfigure (ADC0_BASE、1、0、PIN_IPHASEA); MAP_ADCSequenceStepConfigure (ADC0_BASE、 1、1、PIN_IPHASEA);// AIN5 MAP_ADCSequenceStepConfigure (ADC0_BASE、1、 2、PIN_IPHASEB);// AIN1 MAP_ADCSequenceStepConfigure (ADC0_BASE、1、3、 PIN_IPHASEC | ADC_CTL_END | ADC_CTL_IE);// AIN2