主题中讨论的其他器件:EK-TM4C1294XL、 EK-TM4C123GXL、 TM4C123

来自我的客户:

我们在我们的几款产品上使用了一些 TM4C129 Tiva 微控制器。 我们最近发现,当芯片复位时,Tiva 的 I2C 总线的 SDA 信号会出现低电平干扰的问题。 您能否帮助我们确定这是否是预期行为、以及我们是否需要更改 I2C 配置以安全地处理芯片复位?

我们目前使用以下对 TivaWare API 的调用来配置 SDA 引脚:

GPIOPinConfigure (GPIO_PB3_I2C0SDA);

GPIOPinTypeI2C (GPIO_PORTB_BASE、GPIO_PIN_3);

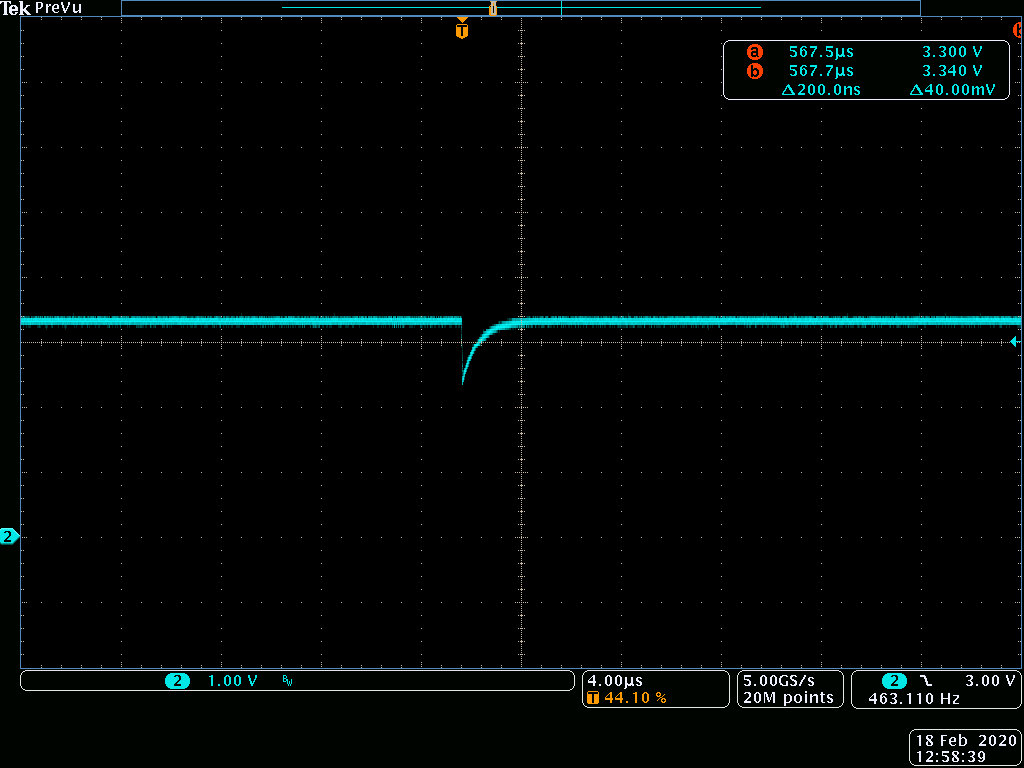

之后、我们的固件发出两种不同类型的复位–软件系统复位(通过调用 SysCtlReset())和看门狗定时器复位(通过允许看门狗定时器超时)。 复位时、SDA 信号暂时驱动为低电平、然后释放、如所附的屏幕截图(示波器通道4)所示。

在发出复位信号之前、我们已经讨论了各种寄存器配置、我们发现在发出复位信号之前调用 GPIOPadConfigSet (GPIO_PORTB_BASE、GPIO_PIN_3、GPIO_Strength _2mA、GPIO_PIN_TYPE_ANALOG)似乎可以解决这个问题。 我们不知道这些寄存器设置为何可以解决此问题,因此我们在未征得您的同意即这是可接受且可重复的修复时,不愿实施此特定修复。 你能给我们提供建议吗?