请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:AM2631 您好!

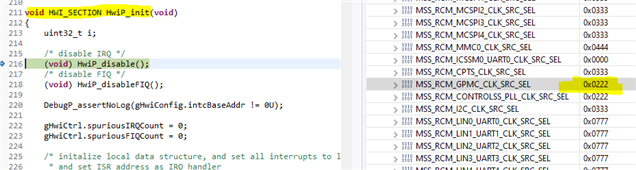

运行 SDK 的 GPMC 示例代码(am263x_09_01_00_41)、我将 在 main 运行前使用 GEL 文件设置 GPMC_CLK_SRC_SEL。 当达到 Hwip_enableFIQ()时,该值会被修改。

是故意的吗?

此致、

哈维尔

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

运行 SDK 的 GPMC 示例代码(am263x_09_01_00_41)、我将 在 main 运行前使用 GEL 文件设置 GPMC_CLK_SRC_SEL。 当达到 Hwip_enableFIQ()时,该值会被修改。

是故意的吗?

此致、

哈维尔

Javier、您好!

Hwip_enableFIQ ()仅更改 CPSR 寄存器的 F 位、不更改 GPMC 的时钟源。 我认为0x2 (系统时钟)是 GPMC 的默认时钟源。

我的测试显示在调用 Hwip_enableFIQ()之前和调用 Hwip_enableFIQ()之后 GPMC 时钟源为0x222 。

在调用 Hwip_enableFIQ ()之前:

调用 FIQ 使能函数后: