工具与软件:

大家好、团队成员:

请检查相关问题的上下文。

您以前回答过:

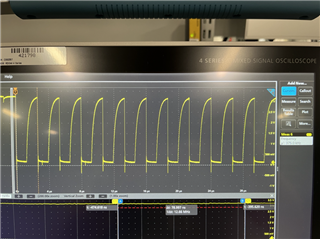

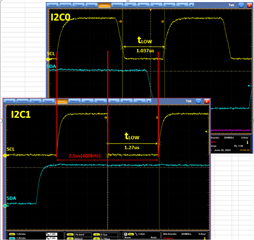

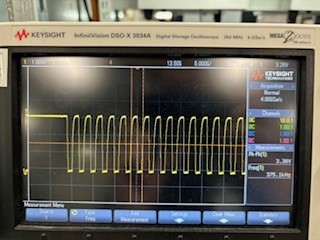

已编程的 I2C SCL 速度和测得的 SCL 速度之间不匹配是由于模块内部同步器的上升/下降时间和延迟造成的。 虽然 I2C CLK 被软件配置为恰好为400kHz、但实际传输速率比在软件中计算和实现的值慢。

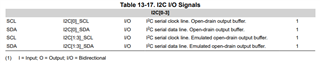

请参阅部分 13.1.2.4.2.1 I2C 计时 中的"Resource Variant" 页面。

我的客户仅看到 I2C0有这一差异、而 I2C1和 I2C2没有看到。 是这样吗?

此致、

Mari Tsunoda.