工具与软件:

尊敬的 TI 团队:

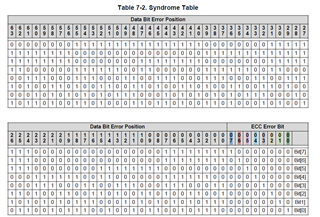

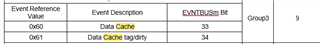

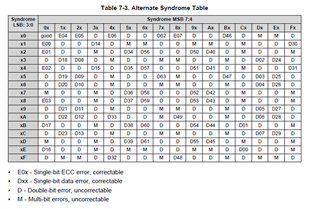

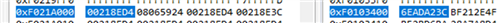

我目前正在使用 TMS570微控制器、并一直在研究其 ECC (纠错码)机制、特别是用于 SRAM 的 SECDED (单错校正双错检测)实现。 我有关于 ECC 代码错误处理的一些问题、尤其是在 ECC 代码本身受到影响的情况下。

我的具体问题是:

-

如果 ECC 代码本身发生一个单位错误(与数据相反)、SECDED 机制如何在错误检测和校正方面处理此问题?

- ECC 机制是否有可能同时检测到一个单位错误和一个多位错误?

- 从校正的角度来看、该机制是否存在基于错误的 ECC 代码错误地纠正数据而不更改 ECC 代码的风险? 这是我的应用程序中的一个主要问题。

-

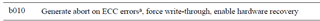

如果可能出现这种情况(即、由于错误的 ECC 代码而导致数据更正错误)、是否有任何策略或机制可用于增强 ECC 代码本身的可靠性?

- 例如、是否在 TMS570架构中推荐了方法或功能来进一步保护 ECC 代码免受位错误的影响?

-

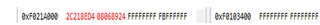

最后、TMS570是对 ECC 代码实现任何类型的冗余(例如、存储 ECC 代码的多个副本并使用多数表决机制)、还是对每个64位数据字仅限于 ECC 代码的单个副本?

非常感谢您对 ECC 代码可靠性作出任何澄清或提出建议!

此致、

汉森