主题中讨论的其他器件:TLV320AIC3120

工具与软件:

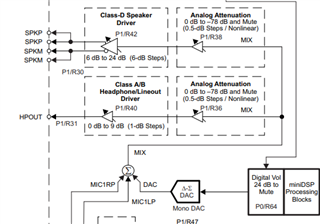

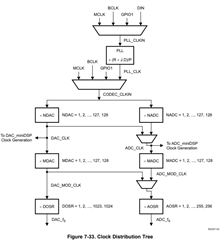

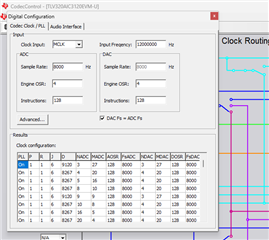

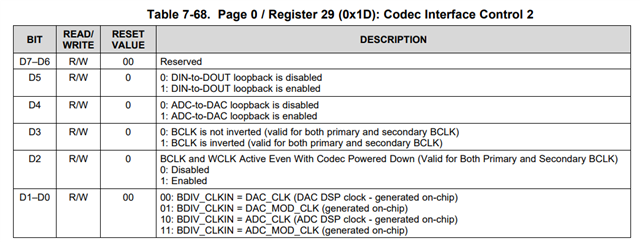

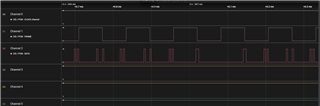

我使用的是 TLV320AIC3120音频编解码器 EVM。 我想控制编解码器、并通过微控制器发送和接收数据。 我能够使用微控制器通过 I2C 校准编解码器的寄存器。 为此、我使用了编解码器中的 TP1和 TP2测试点并 将其连接到了微控制器。 现在、我要检查通过 I2S 线路的数据传输。 为此、我将使用 TP3、TP4、TP5、TP6和 TP7测试点、并将其连接到微控制器。 首先、我需要检查是否 通过 I2S 从微控制器进行数据传输。 在我的场景中、微控制器是主器件。 因此、我已将 I2S Tx 启用为主站、采样频率为8KHz、通道和字长为16。 但是、由于编解码器通过 EVM 内的内部振荡器获得 MCLK、因此微控制器无法提供 MCLK。 我刚刚将微控制器的 MCLK 引脚连接到编解码器 EVM 中的相应测试点、并将其作为控制器中的输入引脚进行连接、以同步微控制器和编解码器的音频子系统。 但仍然有 BCLK 和 WCLK 来自微控制器。 我已尝试发送数据、甚至检查了 BCLK 和 WCLK 引脚、预计 BCLK 为8KHz、WCLK 引脚为128KHz。 "我不知道你在说什么。" 我已经尝试发送一些示例波形文件。 e2e.ti.com/.../8802.main.cIs此配置有任何问题? EVM 中的内部硬件连接是否与微控制器连接冲突? 我甚至可以共享我编写的代码。 请查看它

每个 WCLK 有16位。

每个 WCLK 有16位。