工具与软件:

尊敬的 TI 团队:

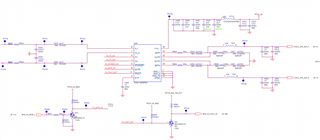

我们的原理图设计如下:

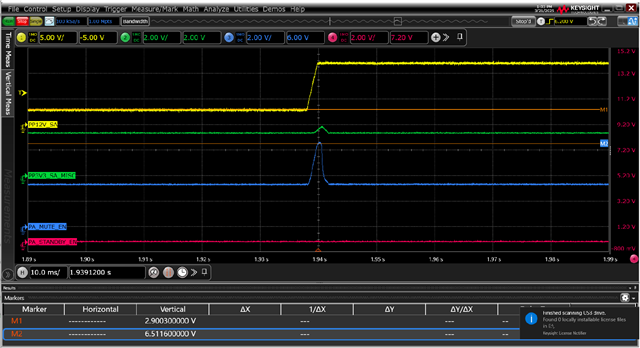

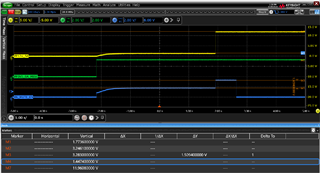

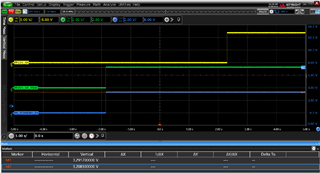

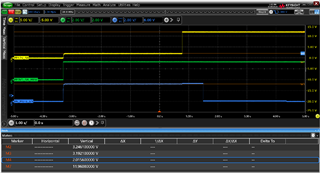

我们测量了 PVDD 和 PA_MUTE_EN、并发现 PVDD 和 PA_MUTE_EN 上存在电压阶跃(PP3V3_SA_MISC 比 PVDD 早大约4秒上电):

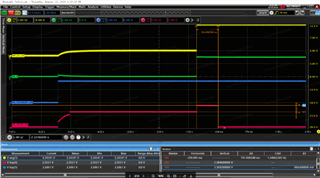

我进行了以下验证:

A:删除了 R5587、PVDD 的中间电压从1.84V 下降到1.44V。

B、删除了 R5587和 R6576、PVDD 上的电压阶跃消失、表示 PVDD 上的中间电压是由从静音引脚和故障引脚到 PVDD 的漏电流引起的。

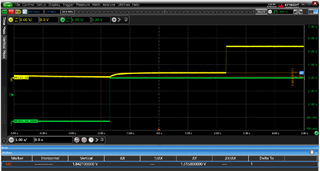

C、删除了 R5587、如 a 波形所示、在 PVDD 上电之前、Mute 引脚的中间电压为1.77V。 因此、我将 R6576更改为100K、静音的中间电压几乎消失。

我的 questios:

1.如何避免在 PVDD 上电之前、从静音引脚和故障引脚的上拉电源漏电流到 PVDD?

2.当用于静音功能的外部上拉电阻为10K 时、为什么在 PVDD 上电之前、外部上拉电阻不能将 MUTE 引脚上拉至3.3V (从 TAS5411-Q1数据表可以看出 MUTE 引脚没有内部上拉或下拉功能)、而将上拉电阻更改为100K 则可以将其上拉至接近3.3V? 如何在 PVDD 上电前避免静音引脚上的中间电压电平?