https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1483501/tlv320aic3263evm-u-tlv320aic3263

器件型号:TLV320AIC3263EVM-U主题中讨论的其他器件:TLV320AIC3263、

工具与软件:

您好!

我使用 TI 的 TLV320AIC3263 示例编解码器系列、但我遇到了一些问题。

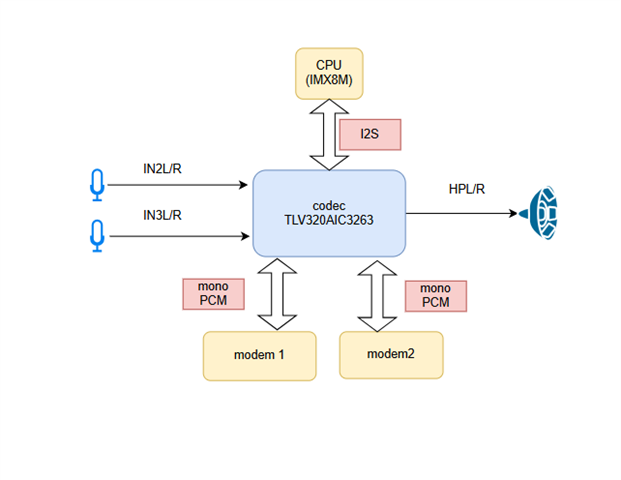

在我的工程中、我需要使用 三个音频接口 :

- 音频接口1 (ASI1) 连接到 处理器 并使用 I2S 协议。 CPU 设置为主器件、编解码器设置为从器件。 (MCLOCK= 48kHz)

- 音频接口2 (ASI2) 连接到 A 调制解调器1 和用途 单声道 PCM。 Modem 1被设置为主器件、而编解码器被设置为从器件。 (BCLK=WCLK=8kHz 2MHz)

- 音频接口3 (ASI3) 连接到另一个电源 调制解调器2 也用于电机 单声道 PCM . 调制解调器2 设置为主器件、编解码器设置为从器件。(BCLK = 2MHz WCLK=8kHz)

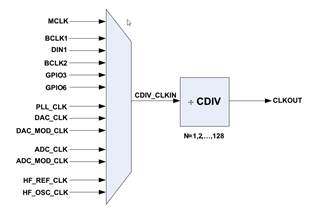

此场景如随附的图所示。

是我要实现的

我想说什么 将从 IN2L/R 和 IN3L/R 接收到的音频信号路由到任何 ASI 接口 动态地配置。 另外、我想说 将从 PCM 和 I2S 接口接收到的音频信号输出到 HPL/R (耳机) .

电流测试设置

首先、我尝试使用测试此设置 两个 ASI 接口 (ASI1和 ASI2)。

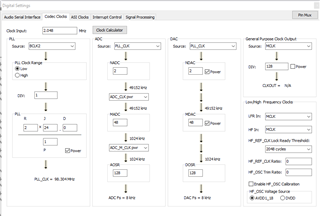

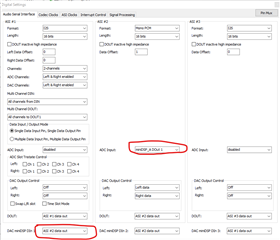

- 我创建了一个 PWF 文件 。 PurePath Studio 、如所附图像中所示。

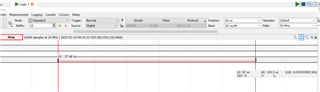

- 我可以听到 单声道 PCM 通过的音频输入 。 .

- 处理器运行 Linux 、使用时

aplay、我可以听到播放过程 ASI1 . - 我可以 录制音频

arecord在上使用 ASI1 功能。

发行

但是、我 无法听到来自 ASI2上 IN2L/R 和 IN3L/R 的音频信号 .

- 吞吐量 IN2L/R 或 IN3L/R 是的 DataOut 引脚上无变化 开始 逻辑分析仪 .

问题

我在哪里可能会犯错? 您能帮助我解决此问题吗?

我配置的寄存器如下:

W 30 7f 00 #选择 Book 0

w 30 00 00 #选择第0页

W 30 06 91 # R=1 J=24 D=0 P=1 PLL 上电 DIV=1

W 30 07 18 # R=1 J=24 D=0 P=1 PLL 上电 DIV=1

W 30 08 00 # R=1 J=24 D=0 P=1 PLL 上电 DIV=1

w 30 09 00 # R=1 J=24 D=0 P=1 PLL 上电 DIV=1

w 30 0A 01 # R=1 J=24 D=0 P=1 PLL 上电 DIV=1

W 30 05 10 # PLL 源 BCLK2

W 30 12 82 # ADC_CLK_Pwr NADC = 2

w 30 13 98 # ADC_M_CLK_pwr mAdc = 24 AOSR = 128

W 30 14 80 # AOSR = 128

W 30 0b 82 # NDAC = 2上电

w 30 0c 84 # MDAC = 4加电

W 30 0d 03 # DOSR 768

W 30 0e 00 # DOSR 768

w 30 04 33 # ADC 和 DAC 拉电流 PLL_CLK

W 30 7f 00 #选择 Book 0

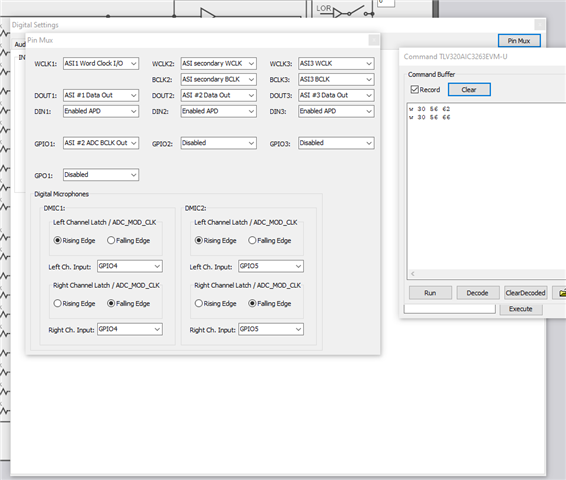

W 30 00 04 #选择第4页

W 30 12 01 #数据偏移

W 30 11 80 #单声道 PCM 16位数据字长

w 30 18 f0 # DAC 输出单声道混合

与布线相关的寄存器配置包含在 PurePath 生成的配置(CFG)文件中。

W 30 00 04 #选择第4页

W 30 76 06 # DAC miniDSP IN1 ASI1数据输出 DAC miniDSP IN2 ASI2数据输出 DAC miniDSP IN13 ASI3数据输出

W 30 08 50 #数据输出控制左/右

W 30 18 f0 #数据输出单声道混合

W 30 28 f0 #数据输出单声道混合

w 30 07 01 # ASI1数字音频输出数据来源于 ADC miniDSP 数据输出1

w 30 17 03 # ASI2数字音频输出数据来自 ADC miniDSP 数据输出2

w 30 27 06 # ASI3数字音频输出数据来源于 ADC miniDSP 数据输出3