主题: TAD5242中讨论的其他器件

工具/软件:

我尝试在1.8V 下使用 AVDD 和 IOVDD 运行 TAD5142

原理图如下所示。

M0-M6根据 I2S 目标数据表进行 strap 配置、AVDD=1.8V、单端线路输出

I2S 信号进入 TAD5142的所有正确信号(16KHz 帧同步、512KHz 位时钟、每帧2x16位)、但 OUT1P 和 OUT2P 上不会产生波形。

OUT1P 和 OUT2P 上有一个1K Ω 下拉。

我没有串联电容器、但应该会出一些东西。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

我尝试在1.8V 下使用 AVDD 和 IOVDD 运行 TAD5142

原理图如下所示。

M0-M6根据 I2S 目标数据表进行 strap 配置、AVDD=1.8V、单端线路输出

I2S 信号进入 TAD5142的所有正确信号(16KHz 帧同步、512KHz 位时钟、每帧2x16位)、但 OUT1P 和 OUT2P 上不会产生波形。

OUT1P 和 OUT2P 上有一个1K Ω 下拉。

我没有串联电容器、但应该会出一些东西。

您好、Ron、

关于上述原理图的一些建议。

我认为根据以上几点、您应该能够使其正常工作。

此致、

Arash

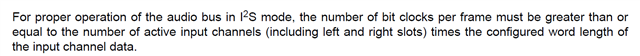

我把表6-3中的文本"字长=32"的意思是" 最大值 对于左通道或右通道、I2S 位流中的字长为32位/样本"

但是、我看到:

这意味着两点:

1) 表6-3中的文本"字长=32"表示" 最小值 对于左通道或右通道、I2S 位流中的字长为32位/样本"

2) 表6-4至6-7需要更正!!

数据表的第6.3.3节明确指出器件具有 PLL、可接受表6-4至6-7中的 BCLK 与 FS 比率