工具/软件:

您好 TI 团队、

现在我们遇到了2个问题、请帮助解决、谢谢。

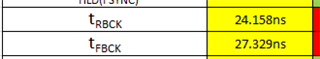

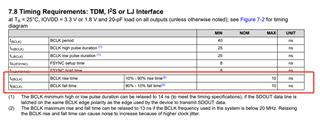

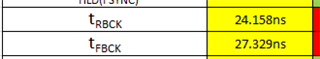

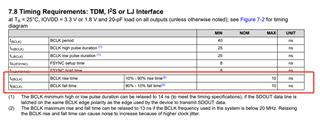

I2S 时钟上升时间和下降时间超出范围、高于20ns

我们的 DUT 的测试数据如下 ?这对性能是否重要、如果我们使其满足 SI 要求、我们需要添加电容器和电阻器以通过 EMC、、我们的 EMC 将失败。

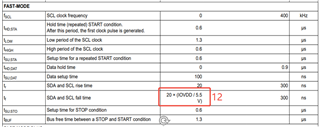

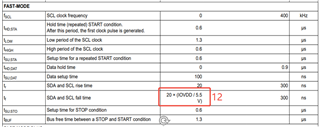

2. I2C 时钟和数据下降时间快,2.937ns 和6.007ns

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好 TI 团队、

现在我们遇到了2个问题、请帮助解决、谢谢。

I2S 时钟上升时间和下降时间超出范围、高于20ns

我们的 DUT 的测试数据如下 ?这对性能是否重要、如果我们使其满足 SI 要求、我们需要添加电容器和电阻器以通过 EMC、、我们的 EMC 将失败。

2. I2C 时钟和数据下降时间快,2.937ns 和6.007ns