工具/软件:

你(们)好

设计了符合以下规格的原理图。

您能回顾一下原理图吗?

- PVDD = 12V

- DVDD = 1.8V

- 与 I2C 相关的信号(I2C_SDA、I2C_SCL)使用电平转换(3.3V–1.8V)电路、因为 SOC 侧使用3V、

Fsw = 768kHz

e2e.ti.com/.../TAS5805M_5F00_schematics_5F00_20250428.pdf

谢谢

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

你(们)好

设计了符合以下规格的原理图。

您能回顾一下原理图吗?

Fsw = 768kHz

e2e.ti.com/.../TAS5805M_5F00_schematics_5F00_20250428.pdf

谢谢

您好:

感谢您的联系。

总的来说、所有元件的布线看起来都很好、但我建议更改一些元件值。

-自举电容应为0.22 μ F

-在输出 LC 滤波器上使用0.68uF 电容器

-为了在电源(PVDD)上进行适当的高频去耦,我会使用1 μ F 和/或.1 μ F 而不是104 pF 或226 pF

-在 AVDD 和 VR_VDD 上、我会使用1uF 电容器

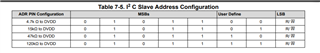

- ADR 应根据下表具有上拉电阻

- PDN 应该有一个上拉电阻器

此致、

Sydney Northcutt