工具/软件:

你好

我尝试将 TLV320ADC3101设置为 I2S 总线的从器件。

I SET BCLK = 1.536 MHz、WCLK = 48kHz 而不使用 MCLK。

MCU 可以输出 BCLK 和 WCLK、而不会出现任何问题。

但是、未接收到 DOUT 信号。

当我使用示波器进行检查时、它处于低电平、没有变化。

RESET 引脚设置为高电平、我使用两个非平衡(单端)麦克风。

下面是寄存器写入的复制结果。

我缺少什么吗? 寄存器写入顺序是否错误?

不使用 MCLK 是错误的吗?

请提供任何建议。

----------------------------------------------------------------------------

TLV320_WriteReg (0x18、0x00、0x00);//页0

TLV320_WriteReg (0x18、0x01、0x01);//软复位

HAL_DELAY (50);

TLV320_WriteReg (0x18、0x04、0x07);// PLL_CLKIN = BCLK

TLV320_WriteReg (0x18、0x05、0x91);//启用 PLL、P = 1、 R = 1.

TLV320_WriteReg (0x18、0x06、0x08);// J = 8

TLV320_WriteReg (0x18、0x07、0x00);// D (MSB)

TLV320_WriteReg (0x18、0x08、0x00);// D (LSB)

TLV320_WriteReg (0x18、0x19、0x03);// CLKOUT = PLL_CLK

TLV320_WriteReg (0x18、0x12、0x81);// NADC = 1、启用

TLV320_WriteReg (0x18、0x13、0x81);// mAdc = 1、启用

TLV320_WriteReg (0x18、0x14、0x80);// AOSR = 128

TLV320_WriteReg (0x18、0x15、0x80);// IADC = 128

TLV320_WriteReg (0x18、0x16、0x04);// miniDSP 抽取= 16

TLV320_WriteReg (0x18、0x1B、0x00);//(从模式、16位、 BCLK/WCLK 输入)

TLV320_WriteReg (0x18、0x1E、0x00);

TLV320_WriteReg (0x18、0x3D、0x01);//页0、寄存器0x3D→PRB_R1

TLV320_WriteReg (0x18、0x0B、0x81);//启用 NDAC、NDAC = 1

TLV320_WriteReg (0x18、0x0C、0x82);// MDAC 已启用、MDAC = 2

TLV320_WriteReg (0x18、0x00、0x01);//页1

TLV320_WriteReg (0x18、0x33、0x68);// MICBIAS1/2 = 2.5V

TLV320_WriteReg (0x18、0x34、0xCF);//左侧= IN2L_P、其他关闭

TLV320_WriteReg (0x18、0x37、0xCF);//右侧= IN2R_P、其他关闭

TLV320_WriteReg (0x18、0x3B、0x5F);//左 PGA

TLV320_WriteReg (0x18、0x3C、0x5F);//右 PGA

TLV320_WriteReg (0x18、0x00、0x00);//页0

TLV320_WriteReg (0x18、0x35、0x10);// DOUT

// ADC 上电

TLV320_WriteReg (0x18、0x51、0xC0)

TLV320_WriteReg (0x18、0x52、0x00)

TLV320_WriteReg (0x18、0x54、0x00)

TLV320_WriteReg (0x18、0x53、0x70)

TLV320_WriteReg (0x18、0x55、0x70)

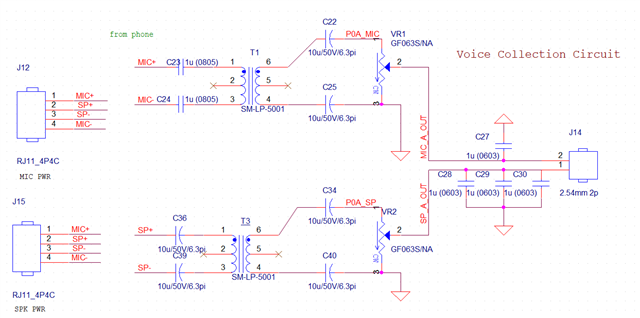

^TLV320ADC3101电路

J14和 J17相互连接。