工具/软件:

尊敬的 TI 团队:

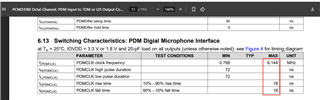

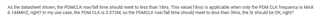

根据数据表所示、PDMCLK 上升/下降时间应满足小于18ns 的要求。 只有当 PDM CLK 频率为 MAX 6.144MHZ 时、该值(18ns)适用、对吗? 在我的用例中、PDM CLK 为3.072M、因此 PDMCLK 上升/下降时间应满足不到36ns、SI 应该可以满足、对吧?

提前感谢您的答复!

BR

sc

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你好 Lakshmi、

感谢您的重播!

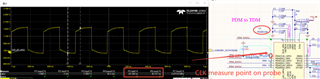

是的、在我的用例中、PDM CLK 为3.072M、由 PCMM3180输出给出。 由于我们在 PDMCLK 上添加了一些 FB/RES 来解决 EMC 问题、因此上升/下降时间(25/30ns)无法满足数据表中所示的规格(18ns)。 因此、我想知道在我的用例(3.072M)中 CLK R/F 时间是否正常。 测量结果如下所示。

BR

成

尊敬的 Lakshmi:

① μ s。 DMIC 数据表对 PDMCLK R/F 时间没有要求。

② μ s。 是、已检查 SI 时序设置/保持时间是否符合数据表规格。

、接近 PCMD3180芯片侧的 PDM R/F 时间不是电路要求、对吧? 一旦 SI 时序设置/保持时间能够满足规格要求。

或者、规范(18ns)要求仅适用于 CLK FR6.144MHZ?

感谢您的帮助。