工具/软件:

我正在通过在 PurePath Studio 中配置测试设计来评估 AIC3254 及其 EVM-K 和 USB-MODEVM 主板。

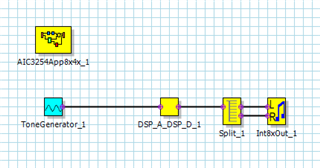

我附录了我当前的 PurePath Studio 设计、该设计使用 AIC3254 的音调发生器之一来生成 2kHz 正弦波、它在进入耳机输出之前通过分离器传递。 下面是该布局的屏幕截图:

在将所有跳线和开关保留为出厂配置的情况下、我在 HPL (TP11) 和 HPR (TP12) 上测量了正弦波、看起来正确。

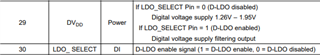

但是、出厂配置中 LDO_SELECT 信号 (SW2) 设置为低电平 (0);如果我将开关更改为高电平 (1)、然后将 USB-MODEVM 连接到我的 PC 并尝试下载配置、则会收到一个错误消息“应用程序下载失败“。 错误:无法连接到硬件“。

根据 SW2/LDO_SELECT 的理解、如果为低电平、则 AVDD 和 DVDD 应提供给 AIC3254;如果为高电平、AIC3254 会生成 AVDD 和 DVDD。 我尝试通过关闭相应的 DIP 开关来禁用 USB-MODEVM 上的 1.8V 输出、但 PurePath 仍然无法连接。

我怀疑 PurePath 生成的配置命令不能为 LDO 供电、如果我查看 SystemSettingsCode、EVM-K 部分没有介绍有关为 AVDD LDO 上电的任何内容、而是在 EVM-U 部分中介绍的:

;-----------------------------------------------------------------------------------

; Configure Power Supplies

;-----------------------------------------------------------------------------------

%%if (%%prop(TargetBoard) == 2)

; AIC3254EVM-U specific configuration

reg[ 1][ 2] = 0xa9 ; Power up AVDD LDO

reg[ 1][ 1] = 0x08 ; Disable weak AVDD to DVDD connection

reg[ 1][ 2] = 0xa1 ; Enable Master Analog Power Control, AVDD LDO Powered

%%else

; AIC3254EVM-K specific configuration

reg[ 1][ 1] = 0x08 ; Disable weak AVDD to DVDD connection

reg[ 1][ 2] = 0x00 ; Enable Master Analog Power Control

%%endif

我有几个问题:

1.如果我要使用 LDO_SEL (SW2) 为高电平、是否需要更改 USB-MODEVM 或 EVM-K 上的任何其他跳线/开关设置?

2.是否有办法告诉 PurePath 它应该生成一个期望 LDO_SEL 设置为高电平而非低电平的配置?

3. 当 LDO_SEL 设置为高电平时、为什么我会断开与 EVM-K 的连接?