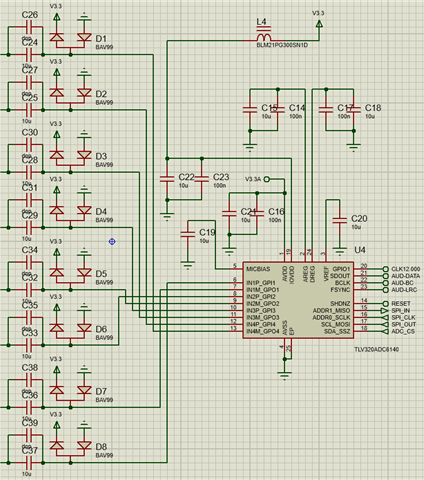

Other Parts Discussed in Thread: TLV320ADC6140

器件型号: TLV320ADC6140

大家好、E2E 专家:

你好。

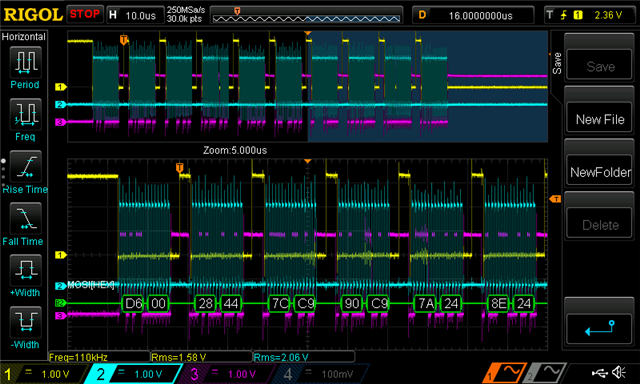

I 通过 SPI 控制 TLV320ADC6140((2MHz 时钟)。 会不时加载不同的配置、其中涉及更新 IC 的以下寄存器。 让我们命名:

配置 A (PGA 增益 8dB):

SpiWrite2 (0xd6、0x00);//AudioSetDecimatorFilter

SpiWrite2 (0x28、0xdd);//AudioSetSampleRate

SpiWrite2 (0x7c、0xc9);//AudioSetDvol

SpiWrite2 (0x90、0xc9);//AudioSetDvol

SpiWrite2 (0x7a、0x20);//AudioSetGain

SpiWrite2 (0x8e、0x20);//AudioSetGain

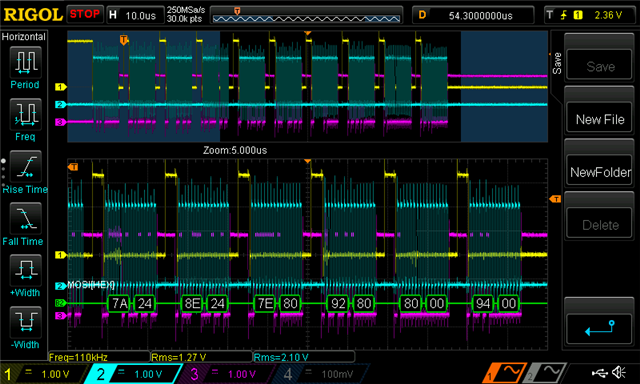

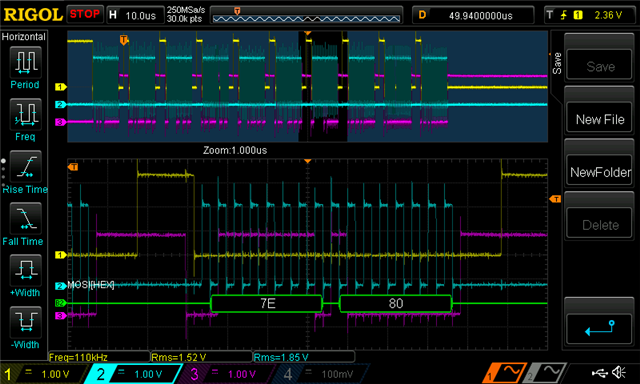

SpiWrite2 (0x7E、0x80);//AudioSetCal

SpiWrite2 (0x92、0x80);//AudioSetCal

SpiWrite2 (0x80、0x00);//AudioSetPhase

SpiWrite2 (0x94、0x00);//AudioSetPhase

配置 B (PGA 增益 9dB):

SpiWrite2 (0xd6、0x00);//AudioSetDecimatorFilter

SpiWrite2 (0x28、0xdd);//AudioSetSampleRate

SpiWrite2 (0x7c、0xc9);//AudioSetDvol

SpiWrite2 (0x90、0xc9);//AudioSetDvol

SpiWrite2 (0x7a、0x24);//AudioSetGain

SpiWrite2 (0x8e、0x24);//AudioSetGain

SpiWrite2 (0x7E、0x80);//AudioSetCal

SpiWrite2 (0x92、0x80);//AudioSetCal

SpiWrite2 (0x80、0x00);//AudioSetPhase

SpiWrite2 (0x94、0x00);//AudioSetPhase

两者之间的差异仅存在于 PGA 值中。

传输按照列出的顺序发送、不修改其他寄存器、ADC 完全正常运行且不会停止、禁用 DRE 和 AGC。

我注意到的是、当当前配置为 A 并发送更新到 B 时、在许多情况下、第一个通道电平大约降低 0.5dB。 此问题可追溯到通道增益校准寄存器 (0x39 = 0x72>>1)。 如果稍后仅更新该寄存器、则问题消失。

在不太可能的情况下、另一个通道有时会降低 0.5dB、或同时提供正确的电平。

从 B->A、A->A 或 B->B 更新时从未出现问题

使用示波器记录 SPI 信号、并进行检查以确保匹配所需的数据。

此致、

公务员制度委员会