Other Parts Discussed in Thread: TLV320AIC3104

器件型号: TLV320AIC3104EVM-K

主题: TLV320AIC3104 中讨论的其他器件

我要使用 TLV32AIC3104EVM-K

我能够播放 USB 音频、并调整 DAC 和 HP 音量设置。 我还可以使用空间立体声功能。

问题:

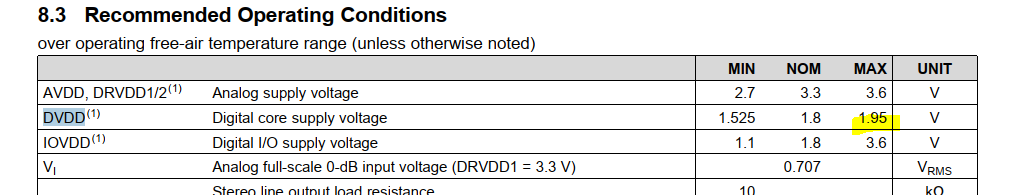

- EVK 默认将 DVDD 设置为 3.3V。 但是、TLV320AIC3104 数据表指出最大电压为 1.95V(见图) 哪一个正确? 我正在完成电路布局、这是重要的信息。

- 我无法获得任何滤波效果。 预设,用户,架子等--它们似乎都不起作用(除了立体声定位器)。 是否需要事先设置一些混频器设置? (我确实禁用了立体定位器)。

- 我无法通过内置麦克风录制或监听任何音频。 我启用了偏置、设置 ADC、混频器、PGA、没有任何成功。 USB 音频接口是否可以实现这一点?

谢谢您、

Brad Stewart、E.E.