https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1082429/pcmd3140-pdm-clk

部件号:PCMD3140您好, PCMD3140可以输出两个 PDM 时钟吗? 同时使用 PDMCLK_GPO1和 GPIO1?

这些时钟是否会被缓冲?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1082429/pcmd3140-pdm-clk

部件号:PCMD3140您好, PCMD3140可以输出两个 PDM 时钟吗? 同时使用 PDMCLK_GPO1和 GPIO1?

这些时钟是否会被缓冲?

让我尝试一个大致的分析。它不准确,但试图帮助设计决策。请告诉我您的想法。

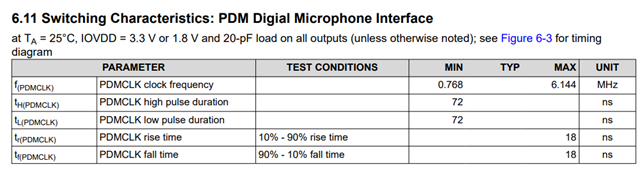

请参阅上图,该图显示了 CLK 引脚的驱动能力。

假设 Vcc 为3.3V,则上升时间为18ns,从10%(0.3V)到90%(3V)。 负载为20p

这意味着电压跨度为2.7V。

假设驱动器是驱动负载电容的恒定电流源。

V=I/C*Ton

I=V*C/Ton

I=2.7V*20p/18n

I = 3mA。 引脚的驱动强度为3mA。

假设麦克风没有长电缆可增加电容。 这是最好的例子。

假设麦克风的每个输入针脚都是15p 负载。 让我们来考虑一个 CLKoutput 驱动器2个多指标类集调查的情况。

2个月为30p 负载。

TR= 2.7V*30p/3mA

TR=27ns TF=27ns

该数据表介绍 了 PDM 时钟的最短高和最短时间为72 ns。 让我们尝试遵守这一规范

T>Thmin+Tlowmin+TR+TF。

t > 72 n+72 n+27 n+27

电话:t>198n

弗克<5.05Mhz。 只要频率低于5.05Mhz,一个驱动2 15p 输入 MICS 的单输出就可以工作,