以前我曾报告 过SRC4392上的DIR存在的问题。

从那时起,我们将SRC4392安装到PCB上,虽然大多数功能似乎都可以正常工作,但我在使用DIR时仍然遇到问题。 我的情况如下:

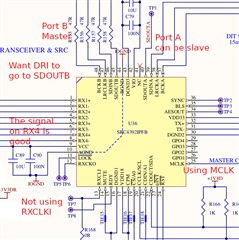

我通过DIT输出音频,然后DIT连接到输入4上的DIR。 端口B I2S总线被配置为从DIR输出输入信号。 单板计算机(SBC)用于生成和捕获音频,如下所示:

SBC ->端口B -> DIT -> DIR ->端口B -> SBC

很遗憾,DIR似乎 不起作用。 时钟未 被锁定,且DIR中没有音频。

我完全不知道此设置有什么问题。 我在另一个问题中向论坛报告的问题与我遇到的问题相同,论坛也没有解决办法。 我有点担心这个芯片在我们的PCB上,我们不能让它作为DIR来工作。

以下是当前寄存器设置:

01:3F

02:00

03:09

04:00

05:29

06:03

07:68

08:00

09:00

0A:00

0B:00

0C:00

0D:1B

0E:17.

0f:22.

10:00

11:00

12:00

13:00

14:00

15:00

16:00

17:00

18:00

19:00

1A:00

1B:00

1C:00

一维:00

1E: 00

1F:00

20:00

21:00

22:00

23:00

24:00

25:00

26:00

27:00

28:00

29:00

2A:00

2B:00

2C:00

2D:00

2E:00

2F:00

30:00

31:00

32:00

33:00

状态如下

12:00

13:00

14:00

15:00

16:00

17:00

18:00

19:00

1A:00