https://e2e.ti.com/support/audio-group/audio/f/audio-forum/576744/pcm5242-audio-converters-forum

部件号:PCM5242主题中讨论的其他部件: TAS5711, TLV320AIC3254

您好,

我有关于 PCM5242 HybridFlow-6 DRC的问题。

问题:当输入信号水平高于阈值(即 -20dB),频率响应不平稳。

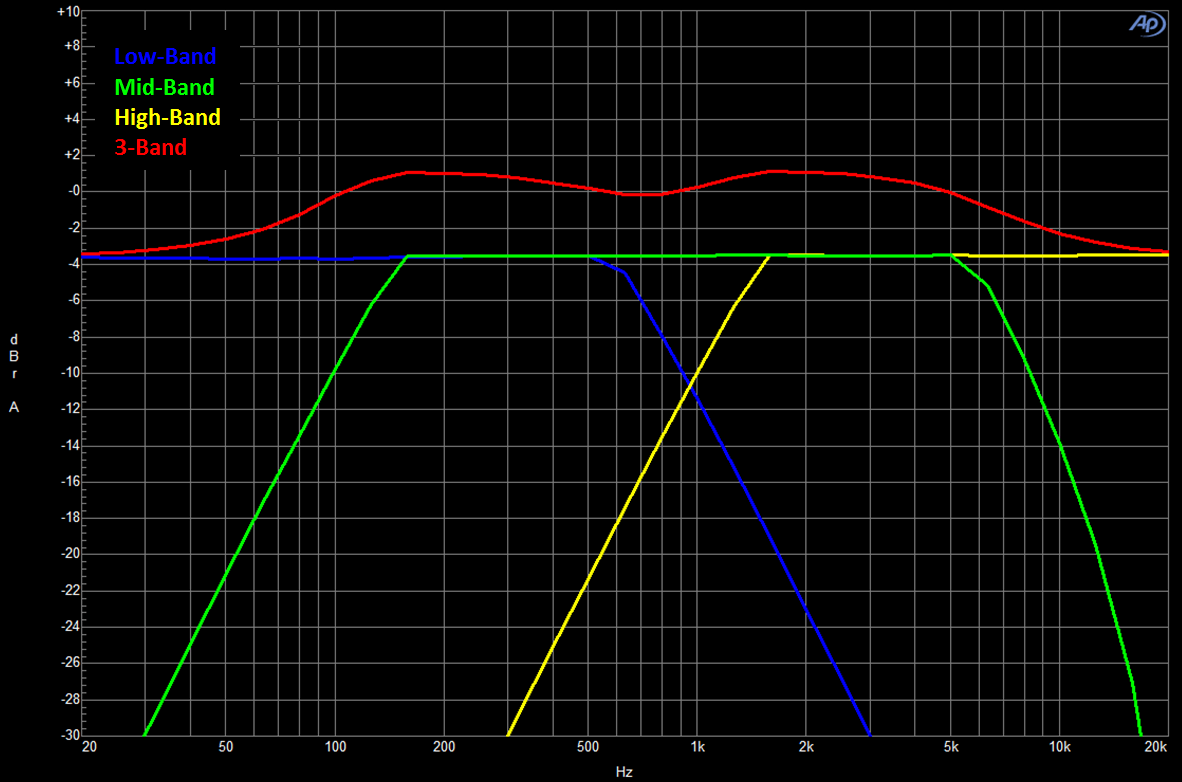

我们的客户正在使用具有DRC区域2比率5的HPF6。 他认为频率响应不应受DRC的影响。 请您提供建议吗?

测试条件:

1.硬件, PCM5242 EVM

2,PSIA输入LRCLK=44.1kHz,MCLK=22.5792MHz,MCLK/LRCLK比率=512

3.接入点测量模式:频率响应,发生器20Hz至20kHz,预扫描=100ms,扫描=2s,电平=-10/-15/-18/-20/-40dBFS

4. PPC 2中的配置使用HybridFlow -6。 DRC区域2比率=1,其他DRC参数和Biquad/DBE..与默认值相同。

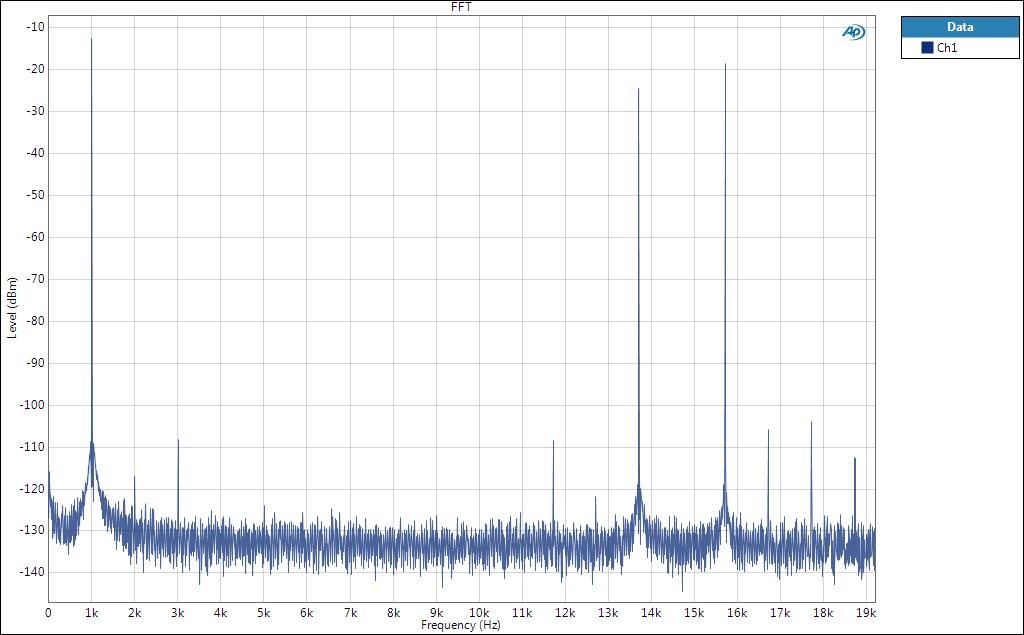

结果:请参阅随附的频率响应捕获。 -10/-15/-18/-20dBFS的频率响应受到影响。

非常感谢,此致,

Tom