您好,

我们一直在尝试让PLL工作一段时间,并取得0进展。

下面是寄存器设置。

正在运行...

第0页REG 0xB:0x45

第0页REG 0xC:0x0

第0页REG 0xD:0x0

第0页REG 0x20:DATA=0x5E clkdet_en=0 ADC_clk_src=1 mst_mode=1 mst_sck_src=0

第0页REG 0x25:0x7

第0页REG 0x26:0x3

PG 0 REG 0x27:Data=0x3F DIV=1/64默认值

第0页REG 0x28:默认情况下,Data=0x1 lock=0 PLL en=1

第0页REG 0x29:P=1/3

PG 0 REG 0x2A:R=1/2

第0页REG 0x2B:J=5

第0页REG 0x2C:D[7:0]=0x16

第0页REG 0x2D:D[13:8]=0x23

第0页REG 0x36:0x0

PG 0 REG 0x70:DATA=0x0 digital_stby=0 SLEE=0 Pwrdn=0默认值

第0页REG 0x71:0x10

第0页REG 0x72:当前设备状态:运行

第0页REG 0x73:=0x4:88.2 -96kHz

第0页REG 0x74:=0x32:SCK_Ratio=256 bck_Ratio=64

第0页REG 0x75:0x0

第0页REG 0x78:0x7

第3页REG 0x12:0x40

-- PLL未锁定。 REG 0x28是0x1

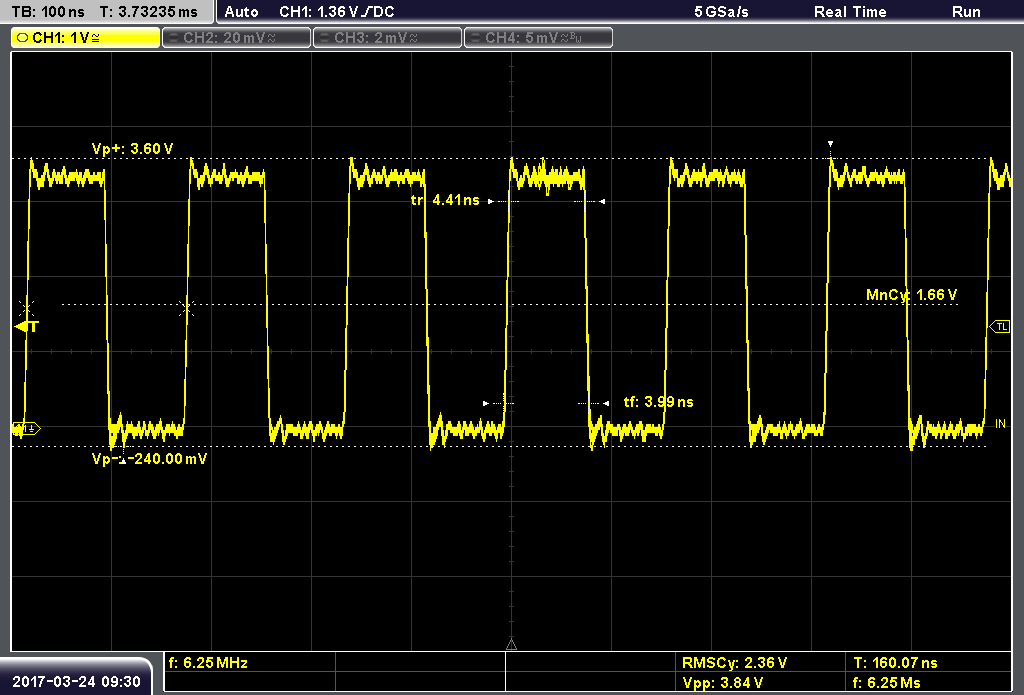

参考时钟为25MHz,正如您从图片中看到的,我们只会看到将25MHz划分为BCK和LRCK。 我假设即使PLL未锁定,我们也会看到PLL的划分(不正确)频率。 但这种情况也没有发生。

有什么想法吗?

谢谢!

Brian