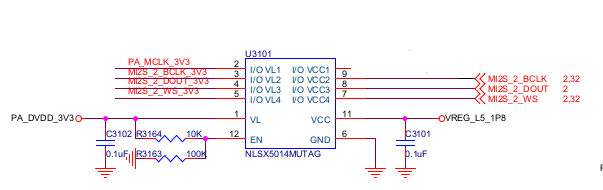

1:TAS5756作为3线PCM模式的从属模式。 没有MCLK,就在我的硬件原理图中连接blck和lrclk,如下所示:

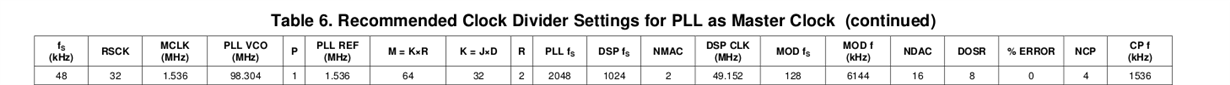

我想补充一点,BCLK是1.536MHZ,LRclk是48kHz,格式是16位。

2:如8.3 中的注释。MCLK,I禁用Page0-R37位1的自动设置模式 ,并忽略,配置寄存器3.4 值为0x12;

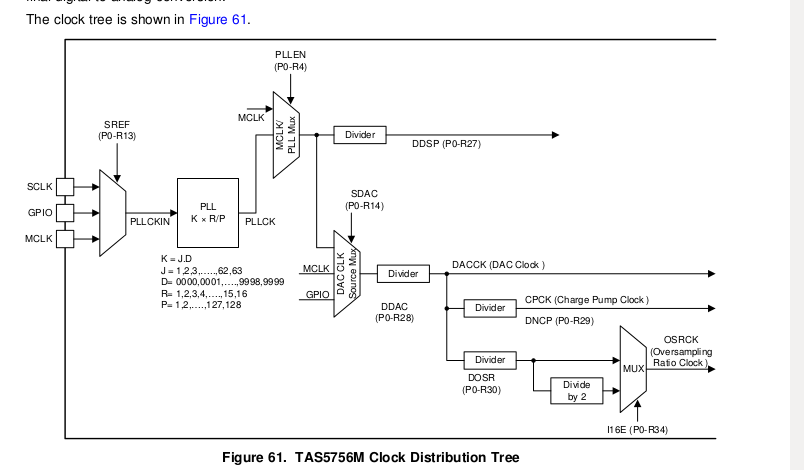

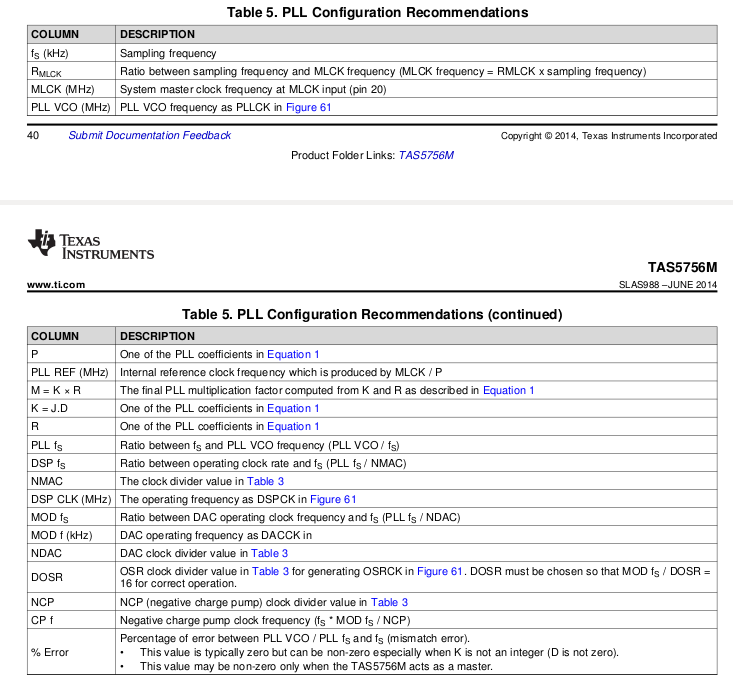

如8.3。3.4 介绍:我应该在下面配置:

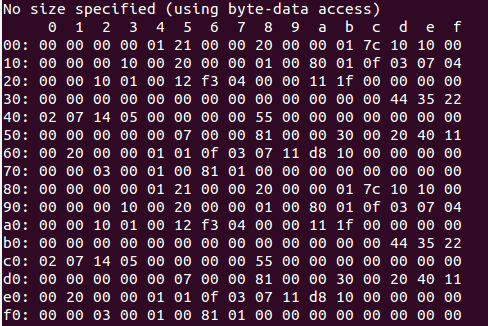

3:我的寄存器配置如下:

Page0:

1:R4——0x00 (禁用PLL)

2:R37——0x12 (忽略MCLK错误报告并禁用自动设置模式)

3:R13——0x10 (PLL参考时钟为BCLK)

4:R20——0x0 (P = 1)

5:R21——0x20 (J =32)

6:R22——0x0 (D==0)

7:R23——0x0 (D==0)

8:R24——0x1 (R=2)

9:R4——0x01(启用PLL)

10:R14——0x10 (DAC时钟源为PLL)Ω

11:R27——0x1 (DSP时钟除法)

12:R28——0xF (DAC时钟除法)

13:R29——0x3 (CP时钟除法)

14:R30——0x7 (OSR时钟除法)

15:R34——0x10此位启用或禁用16x插值模式。(我不知道此位的含义是什么? 可以帮帮我吗?)

4:很抱歉,没有声音。 感谢您查看我的配置,如果有任何错误?