主题: TLV320AIC3105中讨论的其它部件

大家好,支持!

我的客户正在尝试优化TLV320AI3104的功耗。 在他们的设计中,他们使用两个编解码器。 第一个用于从ADC收集数据,通过SAI接口传输数据,然后通过高功率输出从SAI播放到扬声器输出的放大器。

设置和接口规格:SAI:I2S模式,立体声模式,音频16kHz。

安装程序如下所示:

|

注册: |

值: |

|

3. |

0x91 |

|

4. |

0x60 |

|

5. |

0x00 |

|

6. |

0x00 |

|

11. |

0x01 |

|

101. |

0x00 |

|

二 |

0x44 |

|

7. |

0x0A |

|

43. |

0x02 |

|

37. |

0xE0 |

|

41. |

0xA2 |

|

38. |

0x10 |

|

46. |

0x00 |

|

49. |

0x00 |

|

63. |

0x0D |

|

51. |

0x0D |

|

19. |

0x07 |

|

22. |

0x07 |

|

15. |

0x20 |

|

16. |

0x20 |

此设置的总功耗约为12mA。 这是设置所有内容后的值GET,但未提供时钟。

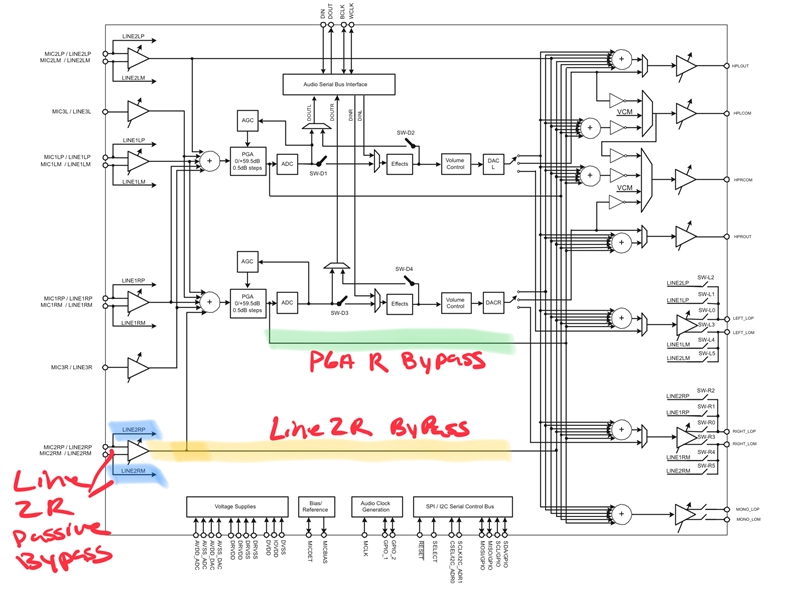

第二个仅用作放大器。 这是由PGA放大的输入,并发送到MCU的ADC的高功率输出。

第二个编解码器的设置规范:

|

注册: |

值: |

|

8. |

0x20 |

|

7. |

0x00 |

|

41. |

0x02 |

|

43. |

0x80 |

|

37. |

0x20 |

|

38. |

0x10 |

|

46. |

0x80 |

|

49. |

0x80 |

|

51. |

0x0D |

|

63. |

0x0D |

|

19. |

0x03 |

|

22. |

0x03 |

|

15. |

0x20 |

|

16. |

0x20 |

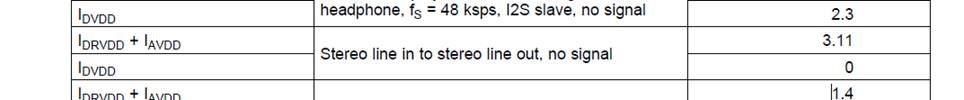

查看TLV320AIC3104 SLAS510F部件8.6 电气特性表:

因此,我希望编解码器的功耗应为3.11mA + HP输出,每个通道约为2mA。 总电流约为7 mA。 但他们仍然获得9.77mA的电流。

您能否帮助我了解功耗高于预期的原因?

谢谢,此致,

Alberto