https://e2e.ti.com/support/audio-group/audio/f/audio-forum/725809/tlv320aic3104-q1-tlv320aic3104-q1

部件号:TLV320AIC3104-Q1大家好,

我正在使用上述部件检查电源引脚(DRVDD,AVDD,IOVDD和DVDD)的漏电流,AVDD引脚读数的电流高于预期,其他引脚的电流处于限值内。

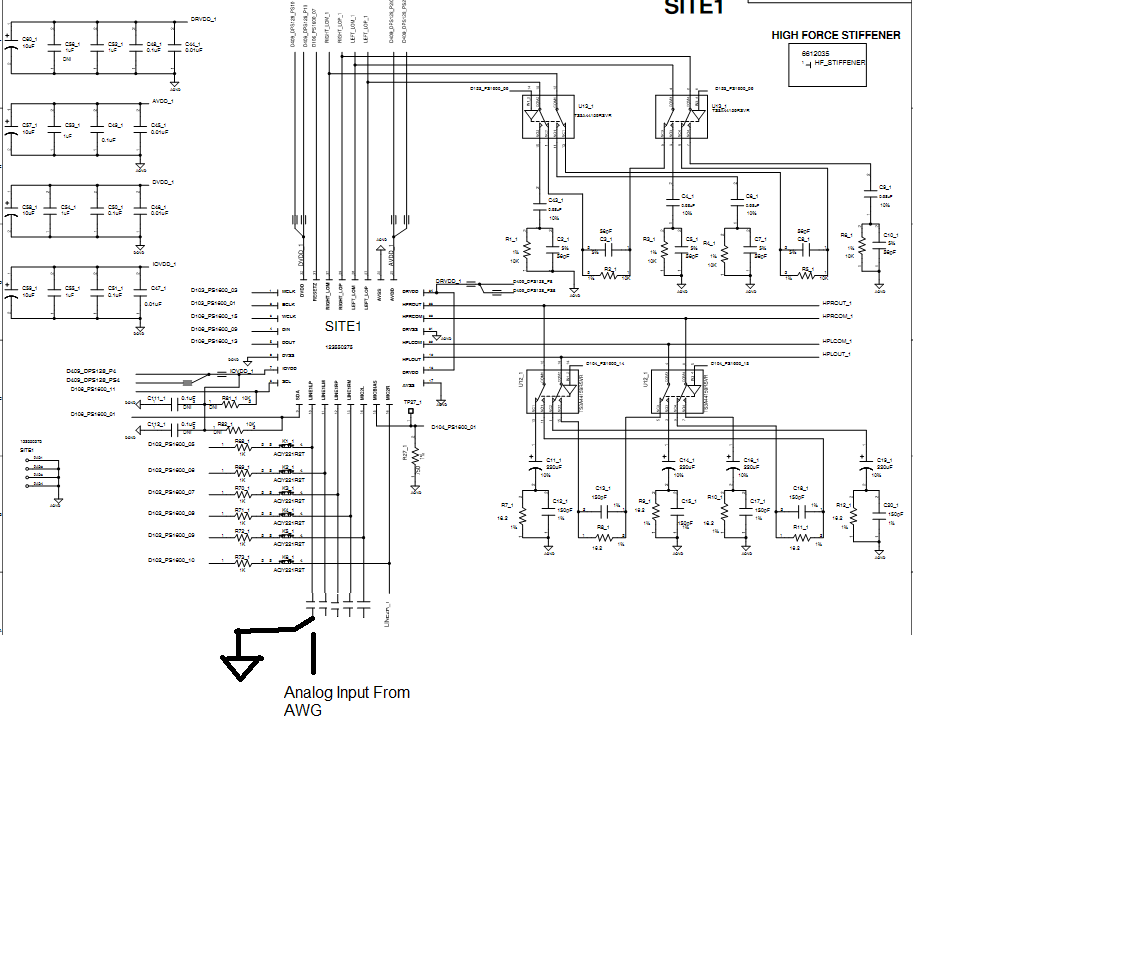

以下步骤允许检查泄漏电流。

1.打开设备电源(AVDD = DRVDD = IOVDD = 3.3V & DVDD = 1.8V)。

2.运行“Reset pattern (重置模式)”(模式包括将650ns的重置针脚设置为“Low (低)”,将650ns的重置针脚设置为“High (高)”,并测量电源针脚之间的电流。

3.重置后,我们可以看到测得的电流在限值范围内。

4.在 电源模式中运行“Power Pattern",设置以下寄存器。

| 注册地址 | 数据 | |

| 0000 0111 (07) | 0010 1010 (2A) | 1.FS(ref)=48 kHz 2.ADC双速率模式已禁用 3.DAC双速率模式已启用 4.LEFT DAC数据路径播放左通道输入数据 5.RIGHT DAC数据路径播放右通道输入数据 |

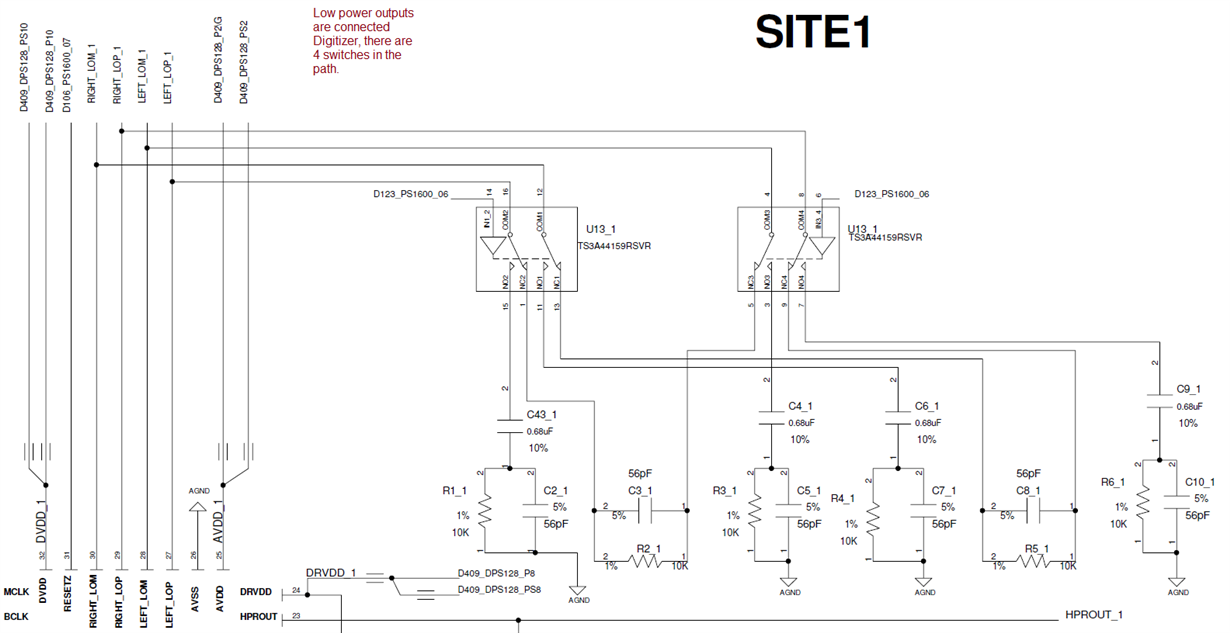

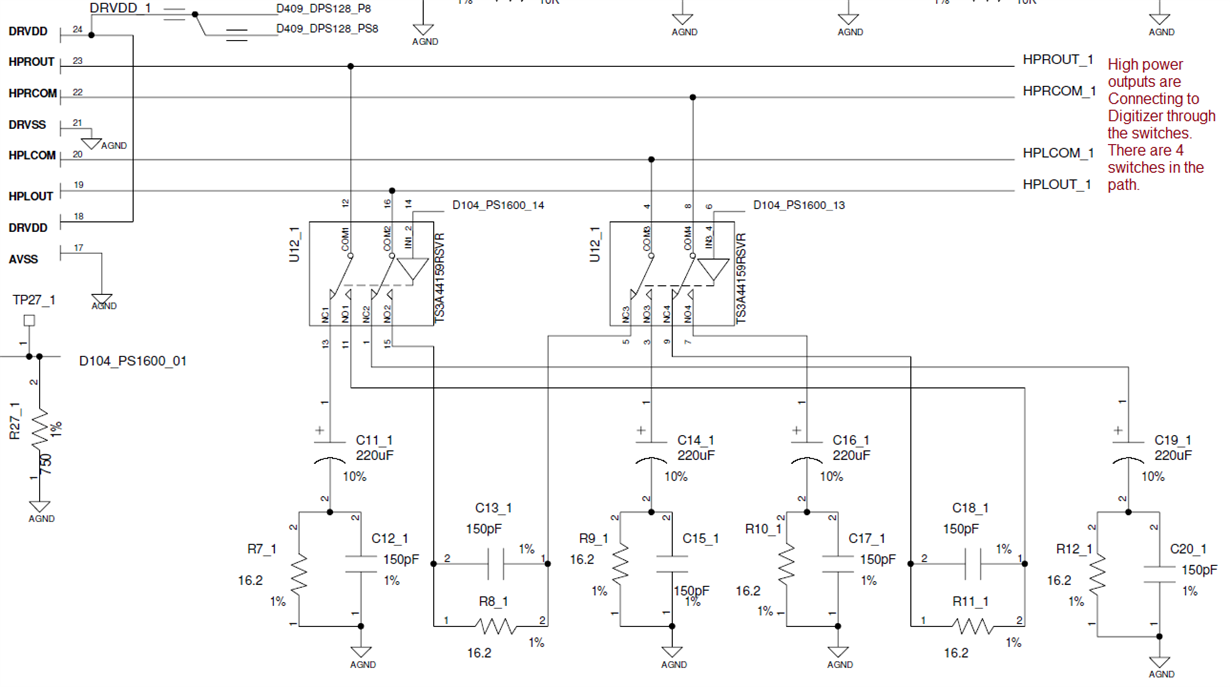

| 0010 0101 (37) | 1100 0000 (C0) | 1.左右DAC通电 2. HPLCOM配置为HPLOUT的差分 |

| 0010 1001 (41) | 0101 0000 (50) | 1.左DAC输出选择DAC_L3路径到左线路输出驱动器 2.右DAC输出选择DAC_R3路径到右线路输出驱动器 3.左和右DAC通道具有独立的音量控制 |

| 0010 1011 (43) | 0000 (00) | 1.左DAC通道未静音 2.左DAC数字音量控制设置为0dB |

| 0010 1100 (42) | 0000 (00) | 1.输出驱动器加电延时控制-驱动器加电时间= 0 μs 2.驱动器提升步长定时控制-驱动器提升步长时间= 0毫秒 |

| 0101 0110 (86) | 0000 1001(09) | 1.LEFT输出电平控制设置为0dB 2.LET_LOP/M未静音 3.LETD_LOP/M的所有编程增益均已应用 4.LET_LOP/M已完全通电 |

| 0101 1101 (93) | 0000 1001(09) | 1.Rright_LOP/M输出电平控制设置为0dB 2.Rright_LOP/M未静音 3.Rright_LOP/M的所有编程增益均已应用 4.Rright_LOP/M已完全通电 |

5.在书写寄存器86和93时,使所附PPT下方的“AVDD”针脚吸入高电流

e2e.ti.com/.../PowerTest_5F00_TLV_5F00_3.pptx

6.特别是写位0,它是左右两侧的电源,导致高电流。

请告诉我您的建议。

谢谢,此致,

Sunil BK