请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

https://e2e.ti.com/support/audio-group/audio/f/audio-forum/760347/tlv320aic3106-tlv320aic3106

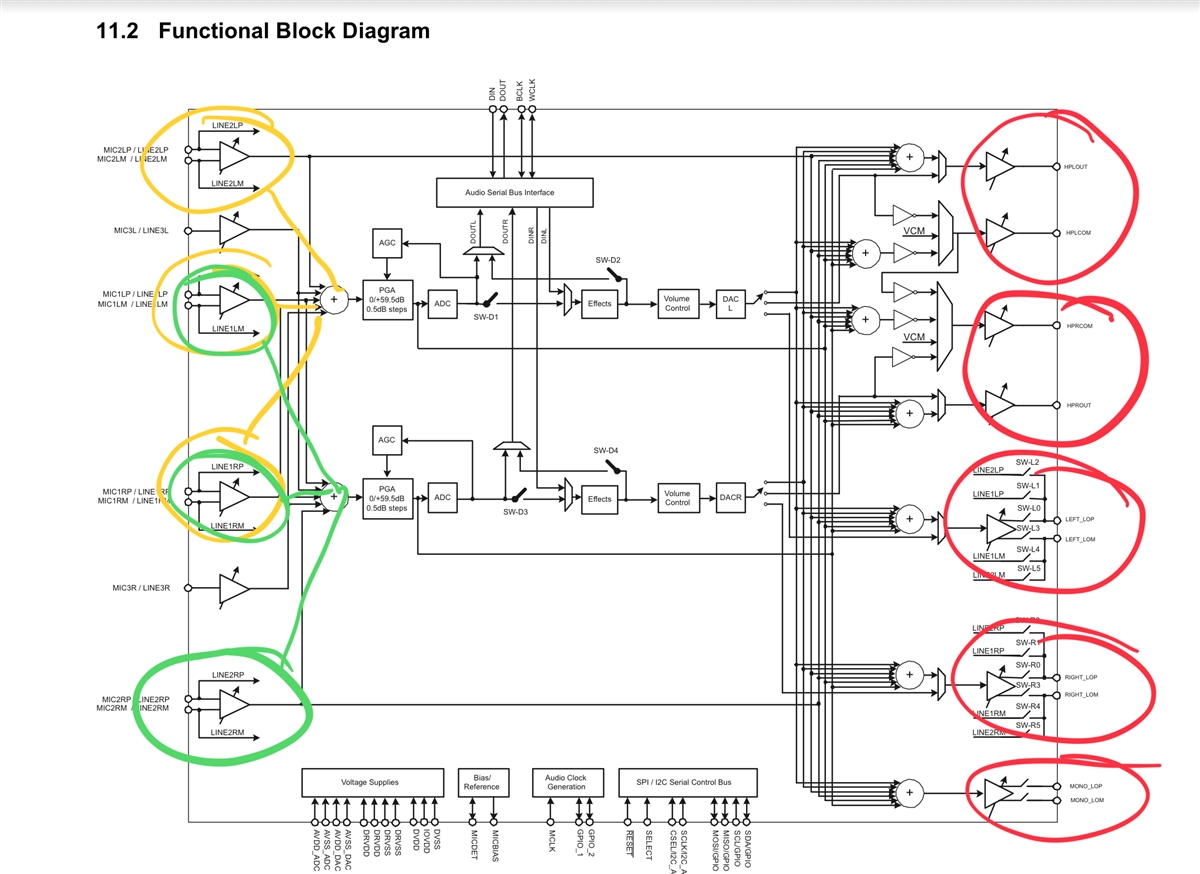

部件号:TLV320AIC3106我想知道该部件有多少完全差分输入和输出。

根据第15页(数据表),它可以有三个全差动线路输出驱动器,根据第33页,它只能有两个全差动线路输出驱动器。

第31页提到它能够将多达三个全差分模拟输入混合到每个ADC PGA中是否是这样的情况?