大家好、

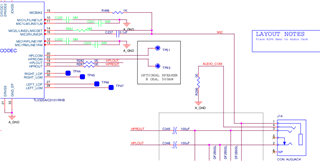

我们将使用具有 Qualcomm 处理器的 tlv320aic3101音频编解码器。 我们将处理器设置为主处理器、将编解码器设置为从器件。

我们的 MCLK 频率为8.192Mhz、BCLK 1.53Mhz、字选48kHz。 我们使用 PLL 来调整从器件侧的时钟。

播放时、我们能够听到比语音更多的噪音。 由于噪音、语音太低、无法听到。 您能帮助找出解决此问题的根本原因吗?

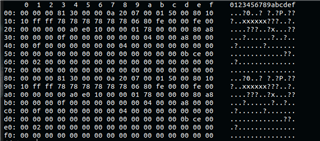

为供您参考、我将介绍我们为回放编写的寄存器和数据。

#Page 0选择寄存器

0x00

#SW 复位寄存器

1 0x00

编解码器采样率选择寄存器 IE;48kHz

2 0x00

#Page 0/Register 3:PLL 编程寄存器 A iE;Q = 16、P = 1

3 0x81

#Page 0/寄存器4:PLL 编程寄存器 B IE;J = 12

4 0x30

#Page 0/寄存器5:PLL 编程寄存器 C (1)

5 0x00

#Page 0/Register 6:PLL 编程寄存器 D

6 0x00

#Page 0/寄存器7:编解码器数据路径设置寄存器

7 0x0a

#Page 0/Register 8:音频串行数据接口控制寄存器 A

8 0x20

#Page 0/Register 9:音频串行数据接口控制寄存器 B

9 0x07

#Page 0/Register 10:音频串行数据接口控制寄存器 C

10 0x00

#Page 0/寄存器11:音频编解码器溢出标志寄存器

11 0x81

#Page 0/寄存器12:音频编解码器数字滤波器控制寄存器

12 0x50

#Page 0/Register 14:耳机/按钮按压检测寄存器 B

14 0x80

#Page 0/寄存器15:左侧 ADC PGA 增益控制寄存器

15 0x10

#Page 0/寄存器16:右 ADC PGA 增益控制寄存器

16 0x10

#Page 0/寄存器20:CM 连接寄存器的左通道模拟输入

20 0x10

#Page 0/寄存器23:CM 连接寄存器的右通道模拟输入

23 0x78

#Page 0/寄存器26:左 AGC 控制寄存器 A

26 0x80

#Page 0/寄存器27:左 AGC 控制寄存器 B

27 0xFE

#Page 0/寄存器28:左 AGC 控制寄存器 C

28 0x00

#Page 0/寄存器29:右 AGC 控制寄存器 A

29 0x00

#Page 0/寄存器30:右 AGC 控制寄存器 B

30 0xFE

#Page 0/寄存器31:右 AGC 控制寄存器 C

31 0x00

#Page 0/Register 36:ADC 标志寄存器

36 0xcc

#page 0/寄存器37:DAC 功率和输出驱动器控制寄存器

37 0xd0

#Page 0/寄存器38:高功率输出驱动器控制寄存器

38 0x0c

#Page 0/Register 40:高功率输出级控制寄存器

40 0x00

#Page 0/Register 41:DAC 输出开关控制寄存器

41 0x01

#Page 0/Register 42:输出驱动器弹出减少寄存器

42 0x78

#Page 0/寄存器43:左侧 DAC 数字音量控制寄存器

43 0x00

#Page 0/寄存器44:右 DAC 数字音量控制寄存器

44 0x00

#Page 0/Register 46:PGA_L 至 HPLOUT 音量控制寄存器

46 0x80

#Page 0/寄存器47:DAC_L1至 HPLOUT 音量控制寄存器

47 0x80

#Page 0/Register 49:PGA_R 至 HPLOUT 音量控制寄存器

49 0x80

#Page 0/寄存器50:DAC_R1至 HPLOUT 音量控制寄存器

50 0x80

#Page 0/寄存器51:HPLOUT 输出电平控制寄存器

51 0x9d

#Page 0/Register 53:PGA_L 至 HPLCOM 音量控制寄存器

53 0x80

#Page 0/寄存器54:DAC_L1至 HPLCOM 音量控制寄存器

54 0x80

#Page 0/Register 56:PGA_R 至 HPLCOM 音量控制寄存器

56 0x80

#Page 0/寄存器57:DAC_R1至 HPLCOM 音量控制寄存器

57 0x80

#Page 0/寄存器58:HPCOM 输出电平控制寄存器

58 0x0d

#Page 0/寄存器60:PGA_L 至 HPROUT 音量控制寄存器

60 0x80

#Page 0/寄存器61:DAC_L1至 HPROUT 音量控制寄存器

61 0x80

#Page 0/寄存器63:PGA_R 至 HPROUT 音量控制寄存器

63 0x80

#Page 0/寄存器64:DAC_R1至 HPROUT 音量控制寄存器

64 0x80

#Page 0/寄存器65:HPROUT 输出电平控制寄存器

65 0x9d

#Page 0/寄存器67:PGA_L 至 HPRCOM 音量控制寄存器

67 0x80

#Page 0/寄存器68:DAC_L1至 HPRCOM 音量控制寄存器

68 0x80

#Page 0/寄存器70:PGA_R 至 HPRCOM 音量控制寄存器

70 0x80

#Page 0/寄存器71:DAC_R1至 HPRCOM 音量控制寄存器

71 0x80

#Page 0/寄存器72:HPRCOM 输出电平控制寄存器

72 0x0d

#Page 0/Register 81:PGA_L 至 LEFT_LOP/M 音量控制寄存器

81 0x80

#Page 0/Register 82:DAC_L1至 LEFT_LOP/M 音量控制寄存器

82 0x80

#Page 0/Register 84:PGA_R 至 LEFT_LOP/M 音量控制寄存器

84 0x80

#Page 0/Register 85:DAC_R1至 LEFT_LOP/M 音量控制寄存器

85 0x80

#Page 0/Register 86:left_LOP/M 输出电平控制寄存器

86 0x0B

#Page 0/Register 88:PGA_L 至 RIGHT _LOP/M 音量控制寄存器

88 0x80

#Page 0/Register 89:DAC_L1至 RIGHT _LOP/M 音量控制寄存器

89 0x80

#Page 0/Register 90:保留寄存器

90 0x00

#Page 0/Register 91:PGA_R 至 RIGHT _LOP/M 音量控制寄存器

91 0x80

#Page 0/Register 92:DAC_R1至 RIGHT _LOP/M 音量控制寄存器

92 0x80

#Page 0/Register 93:Rright LOP/M 输出电平控制寄存器

93 0x0d

#Page 0/Register 94:模块电源状态寄存器

94 0xDE

#Page 0/寄存器95:输出驱动器短路检测状态寄存器

95 0x00

#Page 0/Register 96:粘滞中断标志寄存器

96 0x00

#Page 0/寄存器97:实时中断标志寄存器

97 0x00

#Page 0/寄存器101:时钟寄存器

101 0x00

#Page 0/Register 102:时钟生成控制寄存器

102 0x00