主题中讨论的其他器件:TLV320AIC3120

您好!

我无法使所有 PRB 正常工作。 实际上、我对最后一个 PRB_P25感兴趣、因为"哔声"

时钟由 STM32F7 micro 提供。 当前设置为:

MCLK = 4.096kHz、BCLK = 512kHz、SR = 16kHz、位= 16

PLL 关闭、NADC = 1、mAdc = 2、 NDAC = 1、MDAC = 2、AOSR = DOSR = 128

黄色行中的 PRB 不工作。 由于 DAC 和 PRB 在不同的时钟上运行、因此输出信号看起来像是调制的。

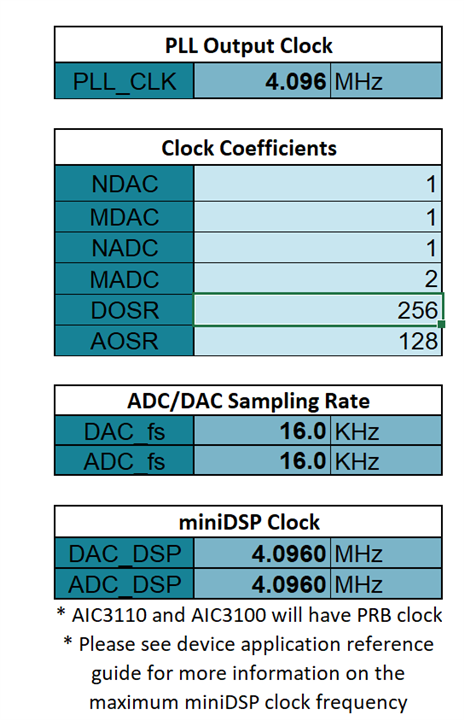

我已使用较大的 OSR 进行了检查、但没有成功:

PLL 关闭、NADC = 1、mAdc = 1、 NDAC = 1、MDAC = 1、AOSR = DOSR = 256

我已经使用 PLL 进行了检查、但这会在输出端产生令人难以置信的噪声:

P=1、R=1、J=24、N=1或48、M=48或1、OSR=128

我有带 TLV320AIC3120的 ACEV 板、所有类型的设置都可以正常工作、如果设置错误、也可以按预期工作。 但我们的设计采用 AIC3110、我没有 EVM。

可以就此提出建议吗? 我觉得资源类在某种程度上是相关的。

谢谢你。