请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:PCM1754-Q1 主题中讨论的其他器件:PCM1754、 CDCS504-Q1

大家好、团队、

我们的客户正在其系统中采用 PCM1754。

输入数据将是 I2S、我们对 SCK 和 BCK 有疑问。

fs 为44.1kHz。

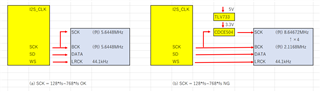

- 由于 SoC 为 SCK 输出时钟、因此它只能输出5.647MHz。

它与数据表中给出的值略有不同、即在 fs = 44.1kHz 时、5.6448MHz 是可接受的 SCK。

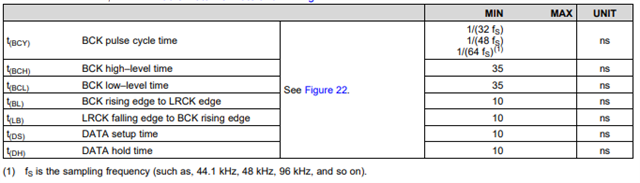

这是否仍然正常? - 在数据表中,它表示如果数据是用 I2S 输出的,则 bck 应为48*FS 或64*FS。

这意味着、如果 fs=44.1kHz、则 bck 应为2.1168MHz 或2.8224MHz。

这些是唯一可接受的 bck 吗?我们可以对 I2S 使用 bck=5.647MHz 吗?

最棒的

Masaru