您好!

我们的团队在某些器件上遇到弹出问题、并非所有器件都存在此问题、并且偶尔会发生此问题。

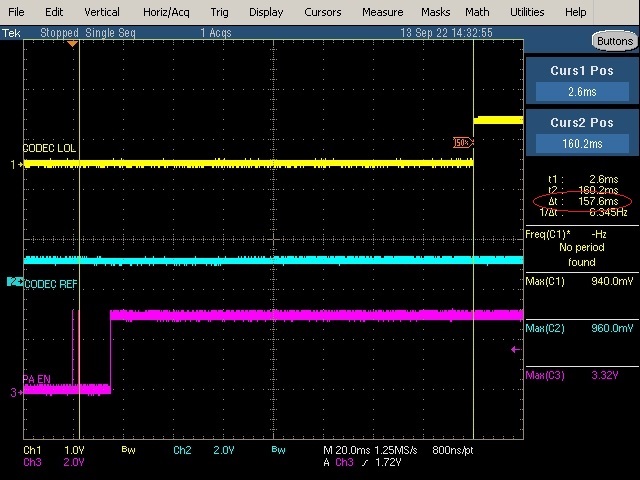

挖掘之后、我发现在 PoP 情况下、软件通过第1页/寄存器9:输出驱动器功率控制寄存器打开 LOL 和 LOR 的电源后、编解码器需要50ms 以上的时间来生成 LOL 和 LOR 输出

而在大多数情况下、LOL 和 LOR 在 SW 命令之后立即输出。

以下是我的调试方法:

1个软件运行到播放例程中

2设置第0页/寄存器63=0xd8。 左侧 DAC 通道上电;右侧 DAC 通道上电;

3设置 第1页/寄存器9=0x0c。 LOL 已通电;LOR 已通电

4在设置 第1页/寄存器9之后、 立即读取相关寄存器(如下所示的值)

弹出案例(标志 REG_P0_37表示 LOL 和 LOR 在当前时间未上电):

[28.042412] JK-->LDO_REG_P1_2:= 0x01 (AVDD LDO 上电;模拟块启用)

[28.043882] JK-->NDAC_REG_P0_11:= 0x81 (NDAC 分压器加电)

[28.044966] JK-->MDAC_REG_P0_12:= 0x81 (NDAC 分压器加电)

[28.046746] JK-->OUT_PWR_CTL_REG_P1_9= 0x0c (将 LOL 和 LOR 设置为加电)

[28.048398] JK-->ADC_FLAG_REG_P0_36:= 0x08

[28.049385] JK-->DAC_FLAG_REG_P0_37:= 0x88

[28.050437] JK-->DAC_FLAG_REG_P0_38:= 0x00

正常/正常情况(标志 REG_P0_37表示 LOL 和 LOR 在当前时间上电):

[38.381675] JK-->LDO_REG_P1_2:= 0x01

[38.382903] JK-->NDAC_REG_P0_11:= 0x81

[38.383797] JK-->MDAC_REG_P0_12:= 0x81

[38.384694] JK-->MDAC_REG_P0_12:= 0x81

[38.385585] JK-->ADC_FLAG_REG_P0_36:= 0x08

[38.386474] JK-->DAC_FLAG_REG_P0_37:= 0xcc

[38.389156] JK-->DAC_FLAG_REG_P0_38:= 0x10

哪些因素或设置会影响 LOL 和 LOR 输出时序?

我还监控了 REF (0.96V)、AVDD (1.76V)、DVDD (1.76V)。 这三个引脚始终接地、我们使用 LDO 来驱动 AVDD 和 DVDD。