大家好、TI 支持团队

一家客户公司正在开发和审查便携式音频放大器。

在回顾期间发生了以下问题、因此我们请求回顾电路图和寄存器转储。

查看条件

[电路条件]

- MCLK、BCLK、LRCK 都使用外部输入。

-22.5792Mhz、2.8224Mhz、44.1kHz。

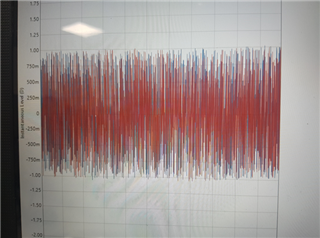

[测试]

-输入1kHz 正弦信号。

- Audio Precision 直接接收 ADC 的 I2S 信号以检查模拟输出。

[输出波形]

[TLV320ADC3101原理图]

e2e.ti.com/.../ADC_5F00_Schematic.pdf

[寄存器转储]

e2e.ti.com/.../TLV320ADC3101_5F00_register-dump.txt

谢谢。

此致、

mj