您好、先生、

早上好。 请帮助查看以下电路。

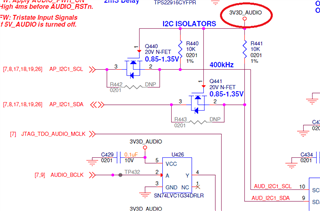

在上电阶段是否存在有关上电序列和 I2C 通信序列的任何问题?

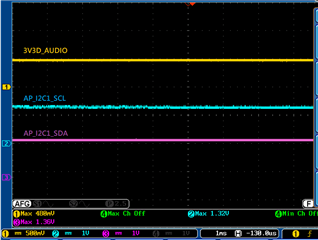

某些电路板在编解码器上电后会出现异常症状(初始化阶段)、即 I2C 时钟在1.8V 上电时将短时间置为低电平、然后 I2C 总线卡在高电平(3.3V)、

主机的 I2C 总线不再正常工作。

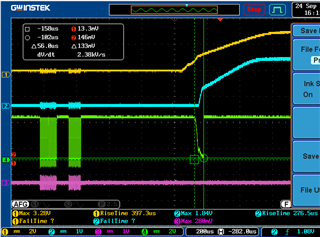

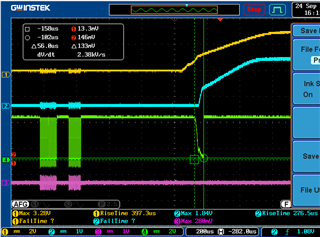

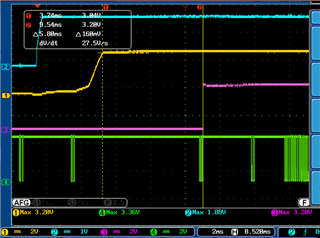

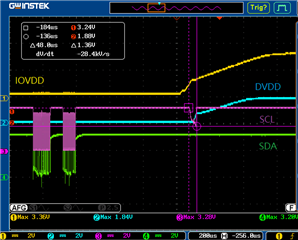

CH1 -> 3V3D_AUDIO

CH2->1V8D_AUDIO

CH4 -> I2C1_SCL

此致、

Joseph

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、先生、

早上好。 请帮助查看以下电路。

在上电阶段是否存在有关上电序列和 I2C 通信序列的任何问题?

某些电路板在编解码器上电后会出现异常症状(初始化阶段)、即 I2C 时钟在1.8V 上电时将短时间置为低电平、然后 I2C 总线卡在高电平(3.3V)、

主机的 I2C 总线不再正常工作。

CH1 -> 3V3D_AUDIO

CH2->1V8D_AUDIO

CH4 -> I2C1_SCL

此致、

Joseph

您好、Joseph、

我不理解"编解码器上电后、即 I2C 时钟在1.8V 时短时间内置为低电平"这一评论。

您是否说主机将在短时间内将 SCL 拉低至1.8V 以为编解码器加电?

对于快速模式、我建议将 R440从10K 更改为2.2K、并使用0欧姆填充 R442、然后检查您是否看到问题。

我不确定我是否了解在该小骤降之前捕获的示波器。

在通道4 (I2C1-SCL)上、即使 3V3D_AUDIO 为低电平、这些 I2C 事务是否为3.3V?

此致。

您好 Pdjuandi、

感谢您的及时响应。

我认为将时钟拉低的不是主机、它看起来像是从机拉伸的时钟。 我们确实使用0欧姆填充了 R442、并且看到了同样的现象。 我认为上拉电阻器是本主题之外的另一个问题、尽管我们需要将上拉电阻器更改为2.2K 以获得更大的驱动电流、具体取决于布线上的寄生电容。

在通道4 (I2C1-SCL)上、即使3V3D_AUDIO 为低电平、这些 I2C 事务是否为3.3V?

->是的、在3V3D_AUDIO 置为高电平之前、主机 I2C 与 I/O 扩展器通信、以将 AUDIO_PWR_ON 置为高电平

此致、

Joseph

您好 Pdjuandi、

感谢您的回复。

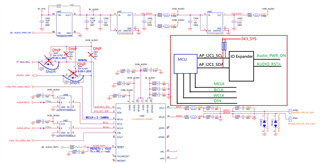

第1次实验。

我们尝试移除器件 PU 和 MOSFET、在 R442和 R443上安装跳线。(如下图所示)。

有关编解码器的控制信号、请参阅红色方框图。

电路的上电顺序为5V_SYS -> 3V3_SYS -> AUDIO_PWR_ON (5V_AUDIO、3V3D_AUDIO、3V3A_AUDIO)-> 1V8D_AUDIO

在这种情况下、I2C 总线仍然停止工作、I2C 电压电平变为1.36V、还会影响 IO 扩展器正常工作。

第2个实验。

将3V3D_AUDIO、3V3A_AUDIO 更改为3V3_SYS。

上电序列变为 5V_SYS -> 3V3_SYS、3V3D_AUDIO、3V3A_AUDIO -> 1V8D_AUDIO

在这种情况下、I2C 事务与器件一起正常工作。

编解码器加电和 I2C 通信序列部分。 这是否意味着编解码器的电源(3V3)与 I2C 主机 PU 同步?

或者、我们是否可以等待所有编解码器的电源就绪、然后等待 I2C 通信(使用 MOSFET 阻止主机 I2C 信号)?

此致、

Joseph

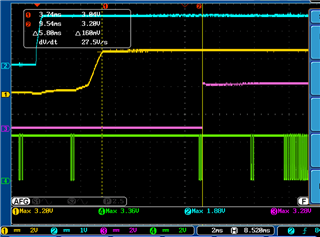

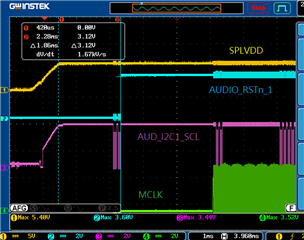

您好 Pdjuandi、

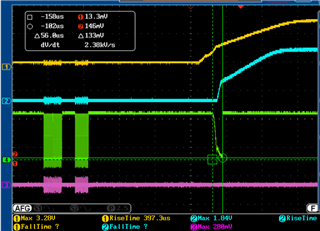

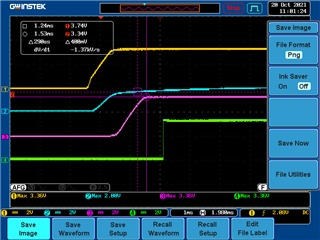

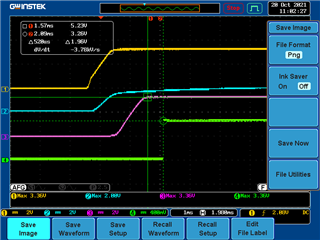

我们已经尝试了编解码器的加电和 I2C 事务序列、如下图1所示、这是成功的情况、但仍然会在该序列上发生故障、如图2所示。 一旦 I2C_CLK 卡在故障时刻、主机 I2C 将不再工作、也无法控制 IO 扩展器以释放 AUDIO_RSTN。

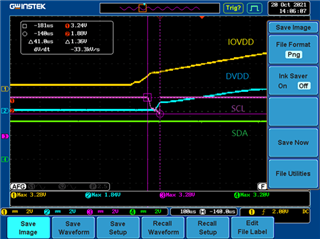

CH1 -> 3V3D_AUDIO、3V3A_AUDIO

CH2 -> 1V8D_AUDIO

CH3 -> AUDIO_RSTn

(图1)

(图2)

此致、

Jospeh

您好、pdjuandi、

这是约瑟夫的助手李秀雄。

很抱歉耽误你这么多天的时间来回答你的问题。

首先、图1中的序列是使用额外导线进行实验的修改电路、我们尝试遵循建议的顺序、即 AVDD 会在最晚斜升。 我们注意到、通过此操作、它似乎降低了某个故障率、但仍然不时失败。

关于您提出的建议、要将复位拉低至少10ns、我相信我们原理图中的复位信号在所有实验中都在5.8ms 左右保持低电平。

如果可以的话,我想向你提出其他问题,以作解释。

尊敬的 Lex:

编解码器要求 IOVDD、DVDD、AVDD 在复位时上拉至低电平至少10ns、以确保数字块处于已知状态。 当这些电源不工作时、编解码器数字节点处于未定义状态。 这就是我在该评论中提到的内容。 因此、我们需要数据表中指定的电源序列、以避免这种情况。

2.这不是时钟拉伸。 如上所述、当这些电源未上电时、数字节点处于未定义状态、 并且可能在电源斜升阶段被驱动为低电平、然而、在电源序列完成后不久(可确保数字内核复位)、此器件将驱动 SCL 和 SDA HiZ。

此致、

Peter

尊敬的 Peter:

我同意您的观点、即在所有电源斜升之前、数字节点处于未定义状态。 对于复位信号、我们确保它在变为高电平之前在5ms 内保持低电平。 实际上、我们已经尝试将导线跳到导线、以确保我们坚持数据表中建议的加电顺序、但症状仍然存在。 一旦发生、它将导致主机连接、整个系统暂停。

让我们来讨论以下主题、以便进一步讨论。

1、在上电过程中、SCL 被驱动为低电平、尽管我们遵循上电序列并在10ns 以上保持低电平。 因此、我们认为该症状与定序无关。

2.我们只是发现,在高温条件下,大约50摄氏度的温度下,这种症状很容易重现。 我们观察到、如果 SCL 降至1.64V 以下、则会导致系统停止。

您能帮助提供其他可能的解决方案吗?

谢谢

尊敬的 Lex:

我们从未看到所有电源均已启动且已应用复位但 SCL 线路上出现毛刺脉冲的情况、我们需要进一步研究。

发生这种情况时、您能否提供 IOVDD、DVDD、SCL 和 RESETZ 的示波器捕获作为起点? 如果您的捕获中可以有更多通道、则添加 AVDD 和 SDA 以实现完整性。 在此调试中、我们希望确保主机不会驱动或启动任何事务。 电源序列完成后、I2C 线路应该已经为 HiZ。

此致、

Peter

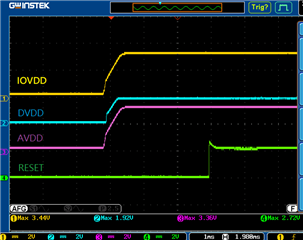

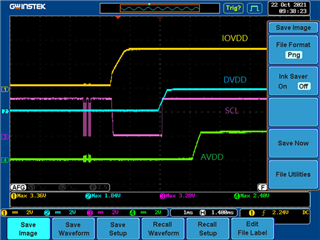

尊敬的 Peter:

我们尝试通过手动尝试来修改电源轨电路、以满足上电流规格。 要求。

在 室温接通测试下、SCL 线路干扰到低症状消失、但在80°C 高温接通测试中仍然出现。 SCL 将切至 低于0.6V 的低电平。

我不确定每个电源轨之间的时间是否足够?

是否有人建议在这些电源轨之间指定延迟时间? 请就此提供建议吗?

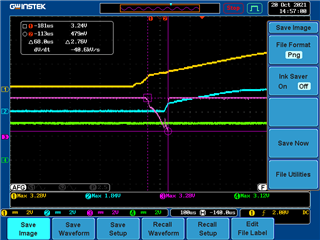

(原始设计上电顺序)

CH1:3V3D_AUDIO

通道2:1V8D_AUDIO

CH3:3V3A_AUDIO

CH4:AUDIO_RSTn

(注意:CH4探头有问题、更改好的探头后电压应为3.3V。)

以调整 TLV320AIC3110上电顺序

在高温导通测试下 SCL 毛刺脉冲至低电平

CH1:3V3D_AUDIO

通道2:1V8D_AUDIO

CH3: SCL

CH4: SDA

此致、

Joseph

尊敬的 Peter:

我想整理一下所有情况、因为到目前为止、情况变得模糊了。

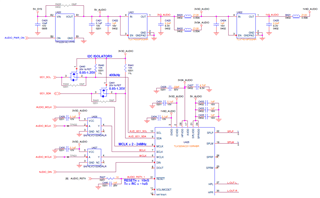

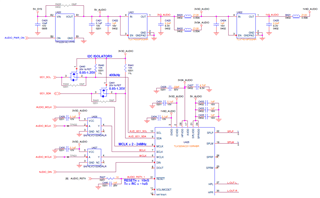

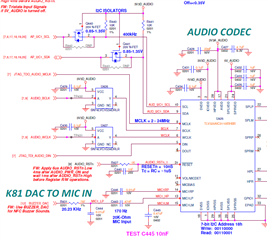

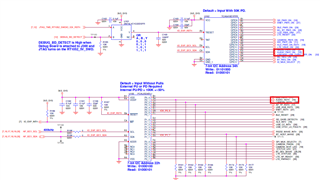

原理图:

电源

音频编解码器

IO 扩展器

AUDIO_PWR_ON 和 AUDIO_RSTN 由 IO 扩展器控制。

IO 扩展器的 I2C 和音频的 I2C 连接到 CPU。

首先、原始设计是同时为所有电源加电、复位在发送 AUDIO_PWR_ON (SPLVDD)信号约2ms 后释放为高电平。

问题是、我们发现连接到音频编解码器的扬声器有时听不到声音。 因此、我们测量了 I2C 信号、发现问题发生在 SCL 下降的情况下。 在高温下、这种下降变得更加严重。 当这个压降出现并且低于1.64V 时、I2C 总线被暂停、无法再工作。 这意味着我们无法命令 IO 扩展器发出 RESET (AUDIO_RSTN)信号、因此从不能将 RESET 释放为高电平。

25°C (SCL 降至1.8V)

56°C (SCL 降至0.48V)

我们尝试在每个电源轨之间进行延迟、很明显、当 IOVDD 上升时、SCL 被拉至低电平、并在 DVDD 跳进时恢复至高电平。 并且确保由于 SCL 上的毛刺脉冲、复位不能释放为高电平。

我认为这种干扰很明显是由 IOVDD 引起的、我很难相信复位与这个问题相关、因为在上电排序期间 SCL 被拉低。 我知道 I2C 只有在释放复位后才是 HiZ。

您能否帮助解释为什么在 IOVDD 启动时 SCL 被拉至低电平?

谢谢你。

尊敬的 Lex:

如上所述、 当 IOVDD 和 DVDD 未完全启动时、数字内核处于未定义状态、需要处于启动状态、并从低电平到高电平的复位转换、以使其进入定义的状态、 在 I2C 情况下、该状态处于数据表复位中提到的 HiZ 状态 部分。

当数字内核处于未定义状态时、它可以被驱动为低电平、如此处所示。

您将需要使这些电源完全启动并将复位状态从低电平状态释放为高电平、以便 I2C 线路可以处于其 HiZ 状态。

您可以尝试将复位引脚与其电流连接隔离、并在为电源供电时将其拉至低电平、一旦电源上电、则将其更改为高电平。

此致、

Peter

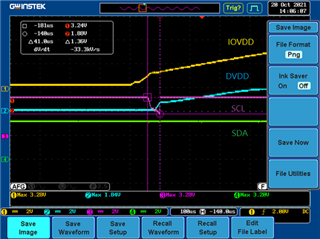

尊敬的 Peter:

我尝试使用另一种方法将复位拉至高电平、而不是由 IO 扩展器控制、结果如下。

如上面的示波器截图所示、即使复位引脚也可以成功地释放为高电平、但仍然会由编解码器停止 I2C 总线。

此后、CPU 仍然无法控制 I2C 总线、因此我认为复位与此问题无关。

[引用 userid="35889" URL"~/support/audio-group/audio/f/audio-forum/1039577/tlv320aic3110-power-and-i2c-communication-sequence-review/3877873 #3877873"]当数字内核处于未定义状态时,可能会驱动为低电平,如此处所示。我是否可以询问此症状是否适用于 TI 的每个编解码器产品?

因为这是我第一次看到这种现象。

如果在释放复位之前 SCL 有可能被拉至低电平、我认为解决这个问题的最佳方法是、将 NMOS 栅极上的电源更改为 AVDD、 这是加电序列中的最新一个、以确保来自 CPU 的 I2C 总线仅在编解码器的电源全部设置后传导至编解码器。

Peter、非常感谢您的帮助和耐心。

尊敬的 Lex:

只有少数类似这个器件的旧器件具有此要求。

您是否更改了上拉值并确保没有任何东西阻止它上拉至 IOVDD?

SCL 上的这个低电平看起来不像一个毛刺脉冲、但更像是保持低电平的东西。

如果电源正常、并且复位转换为高电平、我预计 I2C 将为高阻态。

现在尝试更改栅极电压、甚至绕过它、以确保 I2C 线路为 HiZ。

不用担心,我们随时可以提供帮助。

此致、

Peter

尊敬的 Peter:

我想问、您会建议我们将来更改哪个器件型号、以便在不修改布局的情况下替换我们现在使用的器件型号?

我们确实将上拉值更改为较低的电阻、但仍然相同。

我们尝试从编解码器中切断 I2C、症状消失了。

就短期而言、我们只能在开始时打开音频电源和系统电源、并放弃将编解码器置于睡眠状态的想法。

因为我们没有可控制序列的额外 GPIO、也没有为 I2C NMOS 供电的额外电源。

谢谢

尊敬的 Lex:

此处随附的是一些编解码器器件的简要概述、但这并不是详尽无遗的。

e2e.ti.com/.../AIC_2D00_PCM-products_5F00_scale.pdf

有关完整列表、您可以查看此链接、该链接仅针对音频编解码器进行了排序。

https://www.ti.com/audio-ic/converters/codec/products.html

好的。 然后、我将关闭此案例。

此致、

Peter