https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1038796/pcm1865-common-lrck

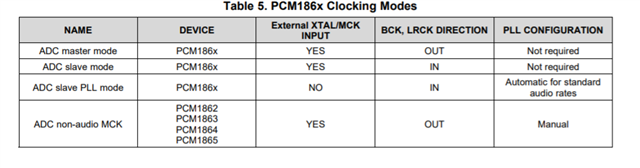

器件型号:PCM1865我在24通道记录仪中使用 PCM1865进行空中交通控制。 为此、我将使用6个 PCM1865器件。 我想将它们连接成3对、3对主器件和3对从器件。 我打算将单个晶振输出分配给主 SCK1输入、然后使用 BCK 和 LRCK 输出来驱动从器件。 所有器件将以48kHz 采样率和24位分辨率驱动。 每个对的输出为 TDM 10通道(4路 A/D 输出及其相关的次级 A/D 通道)。

它们是否是连接这6个器件以使用通用 LRCK 的方法? 由于 TDM 输入被馈送到 FPGA 进行处理、如果它们共用一个公共 LRCK、将节省很多麻烦。

谢谢