我们有一个设计、在该设计中、我们将以8kHz 采样率发送16位样本、以便在 D 类扬声器上播放。 音频质量比较差。 即使在 I2S 总线上发送440Hz 正弦信号、也会导致声音失真。 440Hz 谐波处的峰值实际上高于440Hz 处的峰值本身。 此外、峰值约为8000 - 440 (7560) Hz、表明存在混叠。

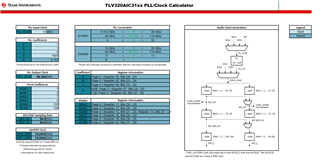

我对任何建议都很感兴趣、但我怀疑问题的至少部分是 DAC 时钟配置、我想做一些澄清。 我们不提供 MCLK、而是将 BCLK (2 * 16 * 8kHz = 256kHz)用作 PLL_CLKIN。 然后、我们按如下方式设置 PLL 值:P=1、R=1、J=32、D=0。 因此 PLL_CLKOUT 为32 * 256kHz = 8.192MHz。 然后、我们使用 NDAC=4、因此 DAC_CLK 为2.048MHz、而 MDAC=4、因此 DAC_MOD_CLK 为512kHz、DOSR=128、因此 DAC_FS 为4kHz。

我的一些问题是:

- DAC_FS 是否应始终与 I2S WCLK 匹配?

- 对于8kHz 采样率、是否有建议的 DOSR 值?

- 由于 TLV320AIC3110没有 miniDSP、如何在其上使用 DAC_CLK?

- NDAC 和 MDAC 之间是否有任何必要的关系?

此外、我看到 PLL 输入支持从512kHz 到20MHz 的时钟、因此我们256kHz 的 BCLK 超出规格。 我想我可以直接将 BCLK 用作 CODE_CLKIN。 我看到、如果使用 PLL、PLL_CLKOUT 必须至少为80MHz、但如果 PLL 未被使用、是否可以使用较低的 CODE_CLKIN? 此外、如果我设置 NDAC=1、MDAC=1和 DOSR=32、我将实现8kHz 的 DAC_FS 以等于 I2S WCLK、但对于8kHz 采样率、32的 DOSR 是否足够?