https://e2e.ti.com/support/audio-group/audio/f/audio-forum/992550/tlv320aic3101-dout

器件型号:TLV320AIC3101您好!

我的客户正在评估 TLV320AIC3101。

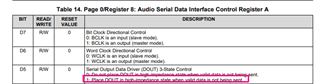

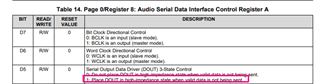

它们将寄存器8 D5位设置为"1"、DOUT 通过电阻器下拉。

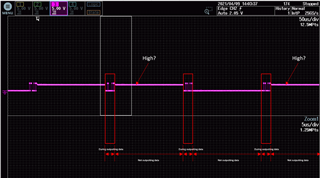

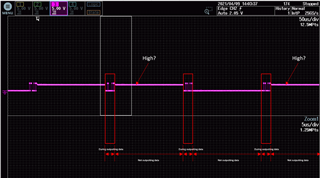

但是、在有效数据未发送期间 DOUT 输出低于高电平。

这是正确的行为吗?

此致、

Kuramochi

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

https://e2e.ti.com/support/audio-group/audio/f/audio-forum/992550/tlv320aic3101-dout

器件型号:TLV320AIC3101您好!

我的客户正在评估 TLV320AIC3101。

它们将寄存器8 D5位设置为"1"、DOUT 通过电阻器下拉。

但是、在有效数据未发送期间 DOUT 输出低于高电平。

这是正确的行为吗?

此致、

Kuramochi

您好、Kuramochi-San、

1.我不确定保持线路为高电平的内部架构、但当发送的最后一位为高电平时、器件将保持 DOUT 为高电平。

2.是,黄色矩形也会显示未发送有效数据的时间。 正如我在前一个应答中所说的、存在两种状态、因为器件将 DOUT 保持在发送的最后一位的同一电平。 您可以看到、就在蓝色矩形之前、发送的最后一位为"1"、因此器件将保持 DOUT 高电平。 在黄色矩形之前、发送的最后一位为"0"、因此器件将线路保持在低电平。

此致、

Aaron Estrada