大家好、团队成员

我们使用 您的 EVM 板、该板可在从站或主 TDM 中正常工作。

但现在工厂已经生产了正式的电路板。

存在硬件 差异:

1) EVM 某些电源使用3.3V、如 AVDD、但我们的板全部电源使用1.8V

2) EVM 使用 模拟 MIC,,我们使用8个 DMIC。

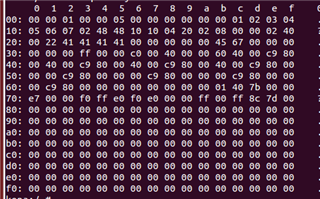

根据文档 tlv320adc3140.pdf、我配置以下寄存器:

从机模式:

0x02 0x01 //电源

0x3c 0x40 //麦克风设置

0x41 0x40

0x46 0x40

0x4b 0x40

0x22 0x41 // GPO 设置

0x23 0x41

0x24 0x41

0x25 0x41

0x41 0x48 //默认48K 12.288M

0x2b 0x45 /GPI 设置

0x2C 0x67

0x73 0xff

0x74 0xff

0x75 0x60

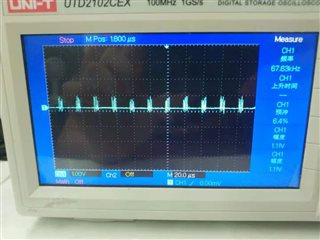

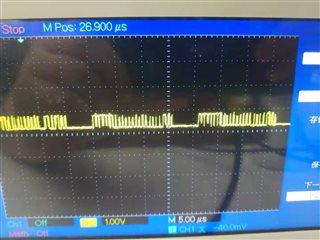

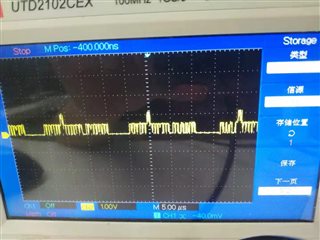

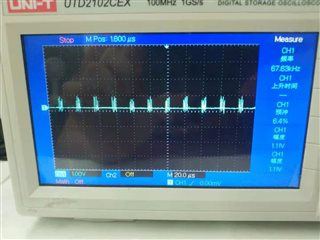

现在、DMIC 可以获取3M CLK 和输出数据。

但记录数据为 NULL、我认为 ADC 输出数据有问题。

ADC 可能输出空数据。

请帮您检查。

谢谢