https://e2e.ti.com/support/audio-group/audio/f/audio-forum/876644/opa1692-opa1692-model-in-ltspice

器件型号:OPA1692主题中讨论的其他器件: TINA-TI

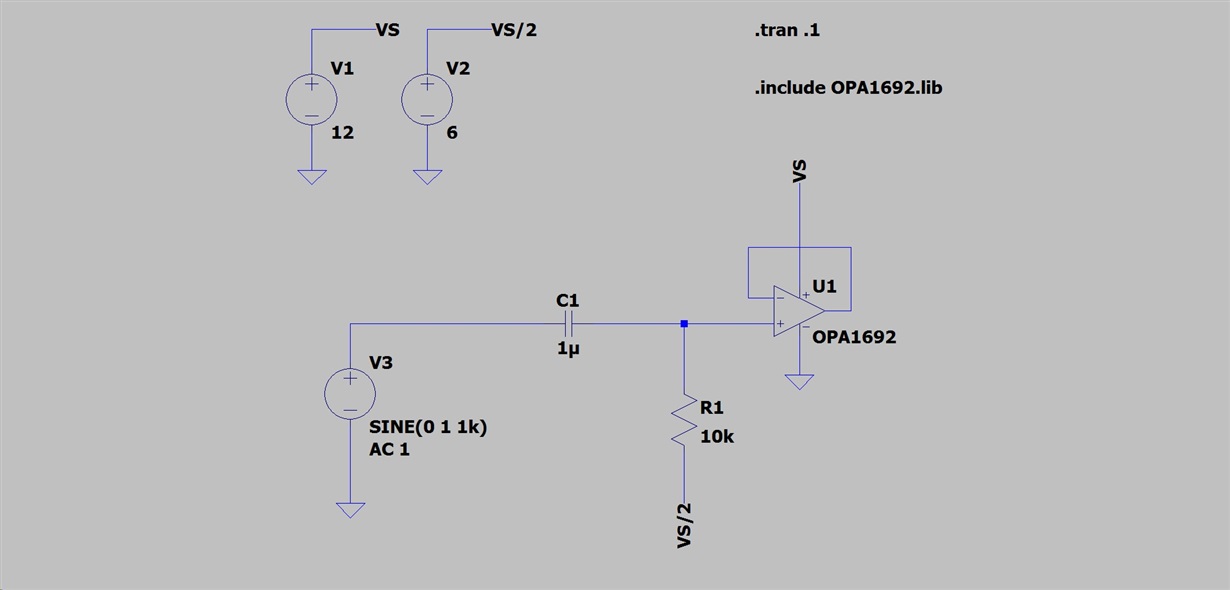

在 LTSpice 中运行 OPA1692仿真后、对于所有连接、错误日志显示"ignoring empty pin current:"

仿真看起来运行正常、但有时会崩溃

我可以在.LIB 文件中更改 LTSpice 的语法是否存在冲突以解决此问题?

忽略空引脚电流:IX (U1:VCM_CLAMP:VIN+)

忽略空引脚电流:IX (U1:VCM_CLAMP:VIN-)

忽略空引脚电流:IX (U1:VCM_CLAMP:VP+)

忽略空引脚电流:IX (U1:VCM_CLAMP:VP-)

忽略空引脚电流:Ix (U1:iqp:VC+)

忽略空引脚电流:Ix (U1:iqp:VC-)

忽略空引脚电流:Ix (U1:iqn:VC+)

忽略空引脚电流:Ix (U1:iqn:VC-)

忽略空引脚电流:Ix (U1:clawp:VC+)

忽略空引脚电流:Ix (U1:clawp:VC-)

忽略空引脚电流:Ix (U1:clawn:VC+)

忽略空引脚电流:Ix (U1:clawn:VC-)

忽略空引脚电流:Ix (U1:cl_amp:VC+)

忽略空引脚电流:Ix (U1:cl_amp:VC-)

忽略空引脚电流:Ix (U1:cl_amp:VIN)

忽略空引脚电流:Ix (U1:ol_sense _opa1692:3)

忽略空引脚电流:Ix (U1:ol_sense _opa1692:4)

忽略空引脚电流:Ix (U1:爪形放大器:VC+)

忽略空引脚电流:Ix (U1:爪形放大器:VC-)

忽略空引脚电流:Ix (U1:爪形放大器:VIN)

忽略空引脚电流:Ix (U1:cl_src:vc+)

忽略空引脚电流:Ix (U1:cl_src:VC-)

忽略空引脚电流:Ix (U1:claw_src:vc+)

忽略空引脚电流:Ix (U1:claw_src:VC-)

忽略空引脚电流:Ix (U1:ger_amp:vc+)

忽略空引脚电流:Ix (U1:gr_amp:VC-)

忽略空引脚电流:Ix (U1:gr_amp:VIN)

忽略空引脚电流:Ix (U1:gr_src:vc+)

忽略空引脚电流:Ix (U1:gr_src:vc)

忽略空引脚电流:IX (U1:VCCS_LIMIT_1:VC+)

忽略空引脚电流:IX (U1:VCCS_LIMIT_1:VC-)

忽略空引脚电流:IX (U1:VCCS_LIMIT_2:VC+)

忽略空引脚电流:IX (U1:VCCS_LIMIT_2:VC-)

忽略空引脚电流:IX (U1:VCCS_LIM_Zo_opa1692:VC+)

忽略空引脚电流:IX (U1:VCCS_LIM_Zo_opa1692:VC-)

忽略空引脚电流:IX (U1:VCM_CLAMP:VIN+)

忽略空引脚电流:IX (U1:VCM_CLAMP:VIN-)

忽略空引脚电流:IX (U1:VCM_CLAMP:VP+)

忽略空引脚电流:IX (U1:VCM_CLAMP:VP-)

忽略空引脚电流:Ix (U1:iqp:VC+)

忽略空引脚电流:Ix (U1:iqp:VC-)

忽略空引脚电流:Ix (U1:iqn:VC+)

忽略空引脚电流:Ix (U1:iqn:VC-)

忽略空引脚电流:Ix (U1:clawp:VC+)

忽略空引脚电流:Ix (U1:clawp:VC-)

忽略空引脚电流:Ix (U1:clawn:VC+)

忽略空引脚电流:Ix (U1:clawn:VC-)

忽略空引脚电流:Ix (U1:cl_amp:VC+)

忽略空引脚电流:Ix (U1:cl_amp:VC-)

忽略空引脚电流:Ix (U1:cl_amp:VIN)

忽略空引脚电流:Ix (U1:ol_sense _opa1692:3)

忽略空引脚电流:Ix (U1:ol_sense _opa1692:4)

忽略空引脚电流:Ix (U1:爪形放大器:VC+)

忽略空引脚电流:Ix (U1:爪形放大器:VC-)

忽略空引脚电流:Ix (U1:爪形放大器:VIN)

忽略空引脚电流:Ix (U1:cl_src:vc+)

忽略空引脚电流:Ix (U1:cl_src:VC-)

忽略空引脚电流:Ix (U1:claw_src:vc+)

忽略空引脚电流:Ix (U1:claw_src:VC-)

忽略空引脚电流:Ix (U1:ger_amp:vc+)

忽略空引脚电流:Ix (U1:gr_amp:VC-)

忽略空引脚电流:Ix (U1:gr_amp:VIN)

忽略空引脚电流:Ix (U1:gr_src:vc+)

忽略空引脚电流:Ix (U1:gr_src:vc)

忽略空引脚电流:IX (U1:VCCS_LIMIT_1:VC+)

忽略空引脚电流:IX (U1:VCCS_LIMIT_1:VC-)

忽略空引脚电流:IX (U1:VCCS_LIMIT_2:VC+)

忽略空引脚电流:IX (U1:VCCS_LIMIT_2:VC-)

忽略空引脚电流:IX (U1:VCCS_LIM_Zo_opa1692:VC+)

忽略空引脚电流:IX (U1:VCCS_LIM_Zo_opa1692:VC-)

以下是 OPA1692 SPICE 模型中的子电路(从北向):

.SUBCKT VOS_LO漂 移_OPA1692 VOS+ VOS-

.Param DC = 2.2141E-04

param POL=1.

.param 漂移= 5.00E-07

E1 VOS+ VOS- Value={DC+POL*漂移*(TEMP-27)}

.end

*

.subckt CLAMP _AMP_HI_OPA1692 VC+ VC- VIN COM VO+ Vo-

.param G=10

GVo+ COM Vo+值={if (V (VIN、COM)>V (VC+、COM)、(V (VIN、COM)-V (VC+、COM))*G)、0)}

GVo- COM Vo-值={if (V (VIN、COM)<V(VC-,COM),((V(VC-,COM)-V(VIN,COM))*G),0)}

.ends CLIG_AMP_HI_OPA1692

*

.subckt OL_SENSE_OPA1692 1 2 3 4

GSW+ 1 2值={if ((V (3、1)>10e-3 | V (4、1)>10e-3)、1、0)}

.END OL_SENSE_OPA1692

*

.subckt FEMT_OPA1692 1 2.

.param FLWF=.1

.param GLFF=2.31893

.param RNVF=165171

.model DVNF D KF={PWR (FLWF、0.5)/1e11}= 1.0e-16

I1 0 7 10e-3

I2 0 8 10e-3

D1 7 0 DVNF

D2 8 0 DVNF

E1 3 6 7 8{GLFF}

R1 3 0 1e9

R2 3 0 1e9

R3 3 6 1e9

E2 6 4 5 0 10

R4 5 0{RNVF}

R5 5 0{RNVF}

R6 3 4 1e9

R7 4 0 1e9

G1 1 2 3 4 1e-6

结束 FEMT_OPA1692

*

.subckt VCCS_EXT_LIM_OPA1692 VIN+ VIN- IOUT- IOUT+ VP+ VP-

.param 增益= 1

G1 IOUT+ IOUT-值={LIMIT (GAIN*V (VIN+、VIN-)、V (VP-、VIN-)、V (VP+、VIN-))}

结束 VCCS_EXT_LIM_OPA1692

*

.subckt VCCS_LIM_3_OPA1692 VC+ VC-IOUT+ IOUT-

.param 增益= 1

.param IPOS = 0.127

.param Ineg =-0.127

G1 IOUT+ IOUT-值={LIMIT (GAIN*V (VC+、VC-)、Ineg、IPOS)}

结束 VCCS_LIM_3_OPA1692

*

.subckt VCCS_LIM_4_OPA1692 VC+ VC-IOUT+ IOUT-

.param 增益= 1

.param IPOS = 0.253

.param Ineg =-0.253

G1 IOUT+ IOUT-值={LIMIT (GAIN*V (VC+、VC-)、Ineg、IPOS)}

结束 VCCS_LIM_4_OPA1692

*

subckt VCCS_LIM_CLAWp_OPA1692 VC+ VC-IOUT+ IOUT-

G1 IOUT+ IOUT-表{(V (VC+、VC-))}=

+(0、208.821e-6)

+(50、7.4e-4)

.ends VCCS_LIM_CLAWp_OPA1692

*

subckt VCCS_LIM_CLAWn_OPA1692 VC+ VC-IOUT+ IOUT-

G1 IOUT+ IOUT-表{(V (VC+、VC-))}=

+(0、200e-6)

+(46,5.81e-4)

+(48、7.31e-4)

+(50、8.04e-4)

.ends VCCS_LIM_CLAWn_OPA1692

*

.subckt VCCS_LIM_IQ_OPA1692 VC+ VC-IOUT+ IOUT-

.param 增益= 1e-3

G1 IOUT+ IOUT- Value={if (((V (VC+、VC-)<=0)、0、GAIN*V (VC+、VC-))}

结束 VCCS_LIM_IQ_OPA1692

*

.subckt VNSE_OPA1692 1 2.

.param FLW = 0.1

.param GLF=0.0135754

.param Rnv=22.3014

.model DVN D KF={PWR (FLW、0.5)/1E11}= 1.0E-16

I1 0 7 10E-3

I2 0 8 10E-3

D1 7 0 DVN

D2 8 0 DVN

E1 3 6 7 8{GLF}

R1 3 0 1E9

R2 3 0 1E9

R3 3 6 1E9

E2 6 4 5 0 10

R4 5 0{RNV}

R5 5 0{RNV}

R6 3 4 1E9

R7 4 0 1E9

E3 1 2 3 4 1

结束 VNSE_OPA1692

*

.subckt CLAMP _AMP_LO_OPA1692 VC+ VC- VIN COM VO+ Vo-

.param G=1

GVo+ COM Vo+值={if (V (VIN、COM)>V (VC+、COM)、(V (VIN、COM)-V (VC+、COM))*G)、0)}

GVo- COM Vo-值={if (V (VIN、COM)<V(VC-,COM),((V(VC-,COM)-V(VIN,COM))*G),0)}

.ends CLAMP LO_OPA1692

*

.subckt VCCS_LIM_GR_OPA1692 VC+ VC-IOUT+ IOUT-

.param 增益= 1

.param IPOS = 35.029

.param Ineg =-35.029

G1 IOUT+ IOUT-值={LIMIT (GAIN*V (VC+、VC-)、Ineg、IPOS)}

结束 VCCS_LIM_GR_OPA1692

*

.subckt VCCS_LIM_1_OPA1692 VC+ VC-IOUT+ IOUT-

.param 增益= 1e-4

.param IPOS =.5

.param Ineg =-.5

G1 IOUT+ IOUT-值={LIMIT (GAIN*V (VC+、VC-)、Ineg、IPOS)}

结束 VCCS_LIM_1_OPA1692

*

.subckt VCCS_LIM_2_OPA1692 VC+ VC-IOUT+ IOUT-

.param 增益= 0.264842

.param IPOS = 17.515

.param Ineg =-17.515

G1 IOUT+ IOUT-值={LIMIT (GAIN*V (VC+、VC-)、Ineg、IPOS)}

结束 VCCS_LIM_2_OPA1692

*

.subckt VCCS_LIM_Zo_OPA1692 VC+ VC-IOUT+ IOUT-

.param 增益= 1e3

.param IPOS = 1e4

.param Ineg =-1e4

G1 IOUT+ IOUT-值={LIMIT (GAIN*V (VC+、VC-)、Ineg、IPOS)}

.ends VCCS_LIM_Zo_OPA1692

*