大家好、

数据表显示了以下 有关检测同步丢失情况的信息。

但是我无法捕捉 到内容(黄色部分) 分裂。

------------------------

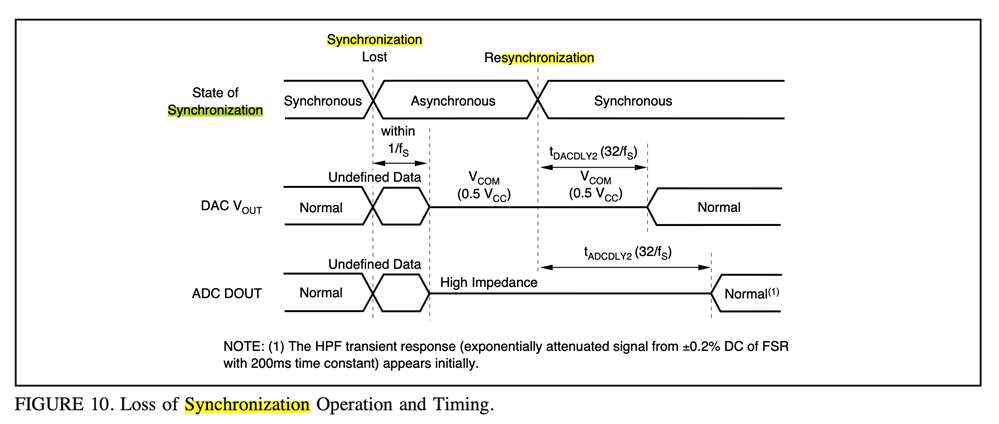

同步要求

PCM3500要求 FS 和 BCK 与系统时钟同步。 包含内部电路以进行检测

FS 和系统时钟输入之间失去同步。 系统之间的相位关系

时钟变化超过±1.5 bck 周期、PCM3500将检测到同步丢失。 检测到后、将显示

DAC 输出强制为0.5VCC、DOUT 引脚强制为高阻抗状态。 这在一次采样中发生

初始检测的时钟(FS)周期。 图10显示了同步操作以及 DAC 和 ADC 的丢失

与之相关的输出延迟。

------------------------

PCM3500是否以1/fs 的频率计算 BCK?

您能否告诉我们如何确认实际的 bck、fs、系统时钟波形(时序图)中是否发生了同步丢失?

此致、

雅丽塔