您好、Sirs、

TLV320AIC3106数据表中的 I2S 信号完整性规格是否由最大50MHz 数据速率定义?

您是否会提供具有3.072MHz 和1.536MHz BCLK 的规格?

3.072MHz BCLK 的326ns 时钟周期、1.536MHz 时钟周期的652ns 时钟周期能否满足 AIC3106's 的要求? 通过计算1/3.072MHz=325.52ns 和1/1,536MHz=651.04ns、测试结果接近。

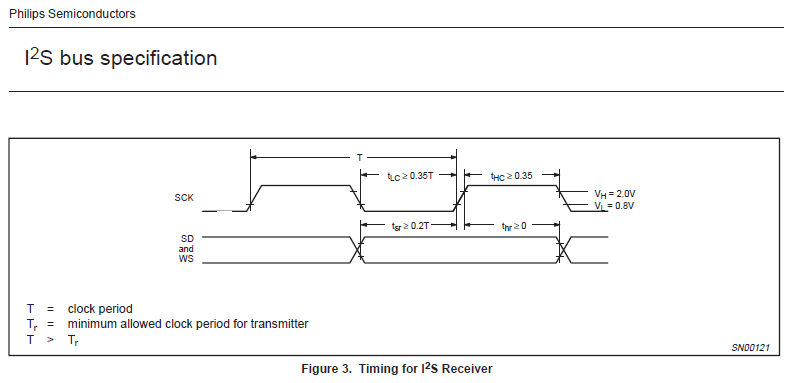

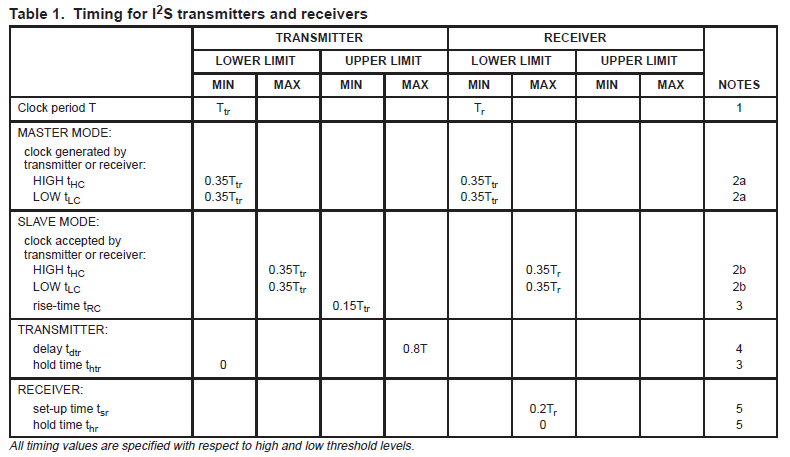

2.我们是否可以将 Philips I2S 规范作为 AIC3106的测试标准?

谢谢、此致、

陈耀恩

08/07/2020