主题中讨论的其他器件:TLV320ADC3101、

您好!

我已使用以下步骤进行配置。

SW_Reset、0x01

Clock_Gen_Multiplexing 0x07 //0b00000111 BCLK

PLL_PR_VAL、0x91 // P = 1 R = 1

PLL_J_VAL、0x30 // J = 48

PLL_D_VAL_MSB、0x00 // D = 0000

PLL_D_VAL_LSB、0x00

ADC_NADC、0x89 //NADC = 9

ADC_mAdc、0x82 //mAdc = 2

ADC_AGSR、0x80 //ASOR = 128

ADC_IADC、0xBC //IADC = 94*2 = 188

ADC_AUDIO_IC_1、0x20 // I2S、20位、无三态

ADC_Processing _BLOCK_SELECTION、0x01

L_ADC_Volume_Control、0x00

MICBIAS_Control、0x00

L_ADC_INPUT_SELECING_L_PGA、0xF3

L_Analog _PGA_Setting、0x00

ADC_Digital、0x80

ADC_F精细_音量_控制、0x08

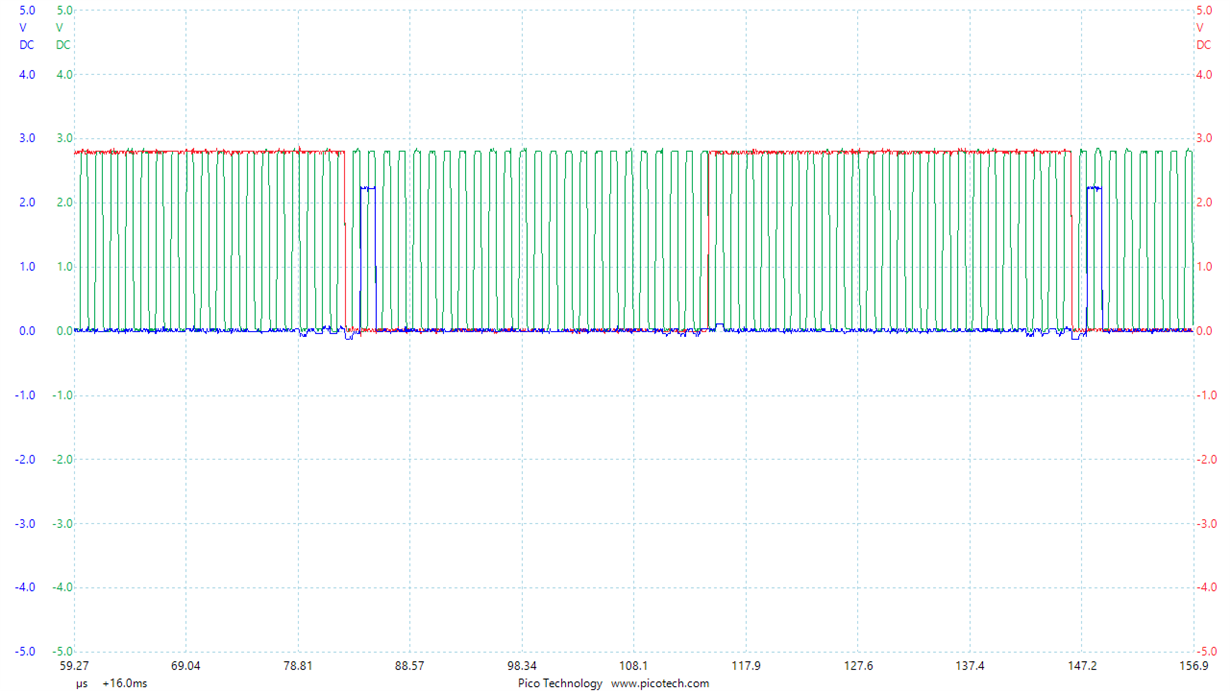

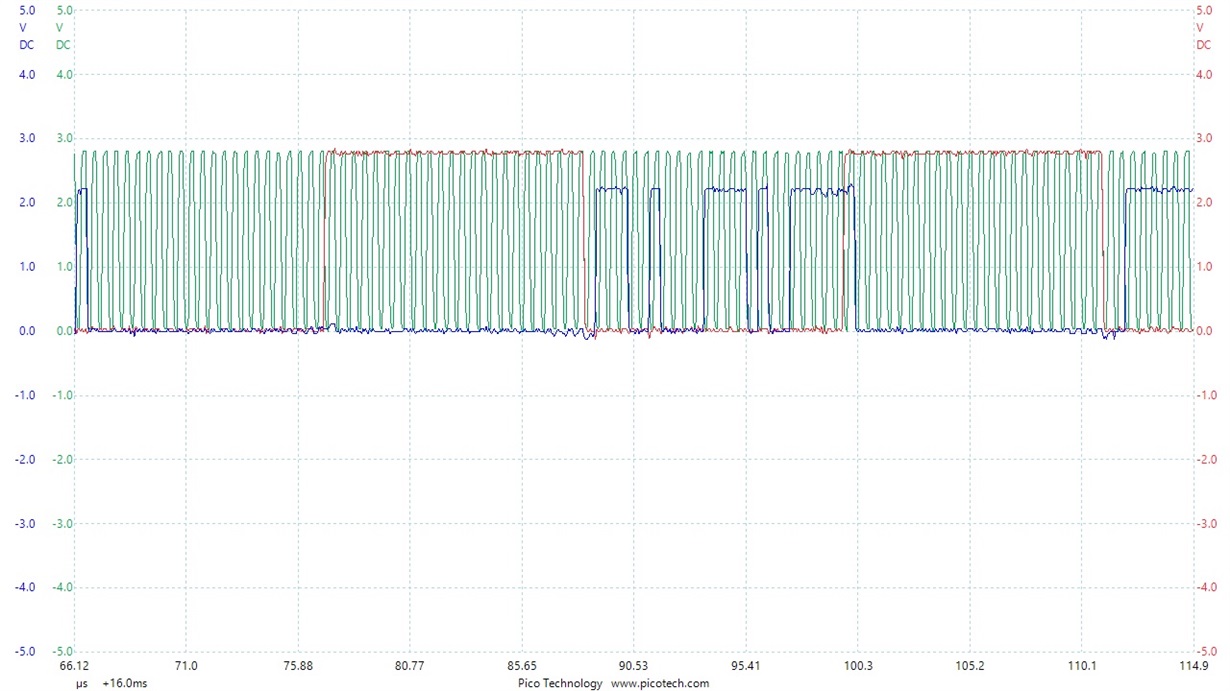

BCLK = 2.133MHz、LRCK = 44.5KHz。 我将 ADC 的输入作为1KHz 正弦波处理、偏移为100mVpp 和50mV。 记录的数字原始输出似乎是噪声。

如果上述配置可行,并且如果我将20位字长更改为24位而不进行任何其他更改,您能不能再进行吗?