https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1163455/tas2505-no-output-sound-issue

器件型号:TAS2505大家好、

我的客户发现没有声音输出、我们现在没有要调试的 EVM

您是否会帮助在此方面进行调试? 它们非常紧急

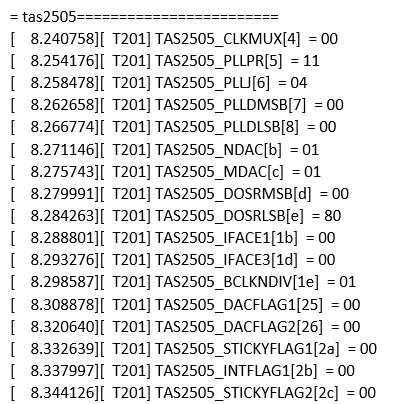

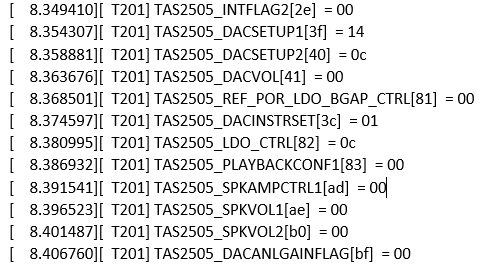

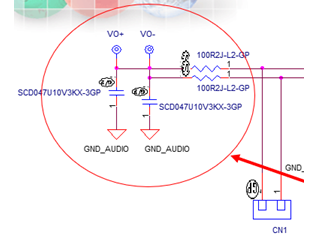

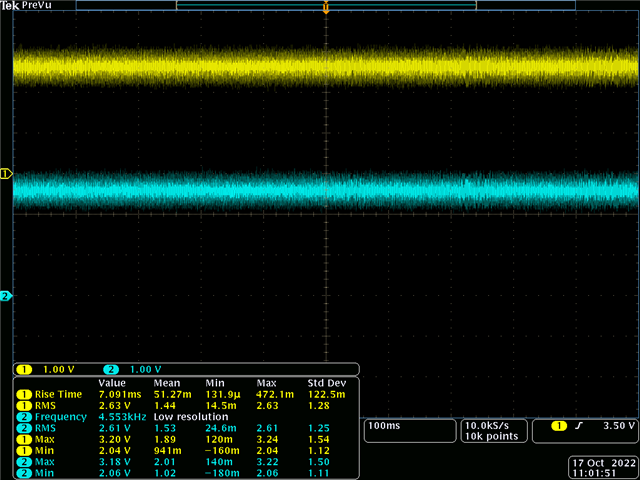

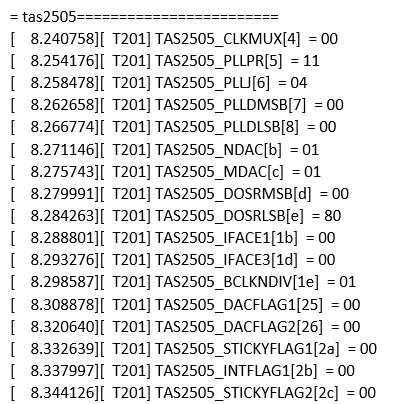

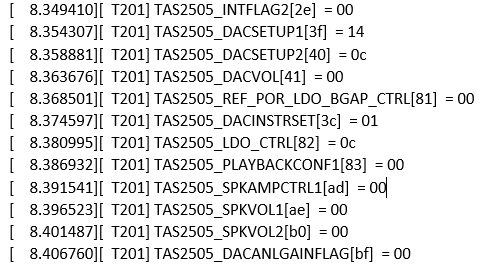

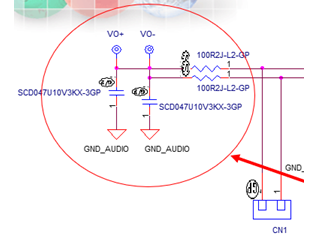

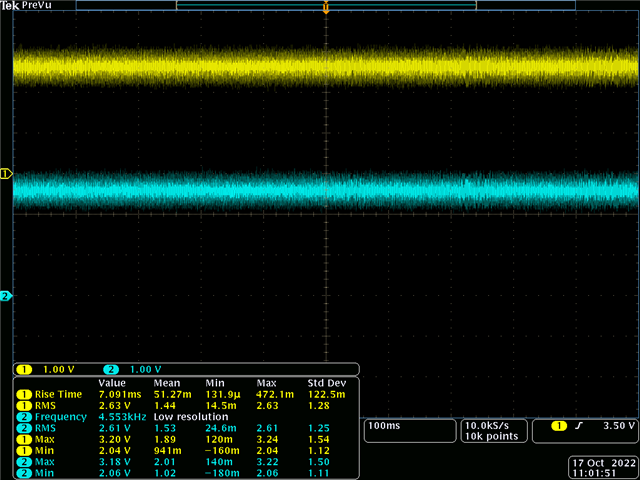

下面是原理图、I2C 日志和输出波形、

它们在 低通后的这两个点进行测量、

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1163455/tas2505-no-output-sound-issue

器件型号:TAS2505大家好、

我的客户发现没有声音输出、我们现在没有要调试的 EVM

您是否会帮助在此方面进行调试? 它们非常紧急

下面是原理图、I2C 日志和输出波形、

它们在 低通后的这两个点进行测量、

您好、Fred、

我对原理图有一些问题、并进行测试:

此致、

-Ivan Salazar

应用工程师

您好、Fred、

您是否还可以共享输入时钟频率以仔细检查寄存器配置? 我们将需要 MCLK (如果使用)、BCLK 和 WCLK。

关于 LDO_SEL 引脚、有时我们鼓励客户不要使用内部 LDO、因为在某些特定应用条件下、某些已知问题会影响一些器件。 这将在即将发布的新版本上进行处理。

但是、如果在所有器件上观察到您的问题、则它不应与此 LDO 相关、您仍应能够使用它。

此致、

-Ivan Salazar

应用工程师

您好、Fred、

查看 I2C 日志后、似乎不正确:

他们可以使用 GUI 示例脚本作为基准:

# Playback Class-D # Page switch to Page 0 W 30 00 00 # Assert Software reset W 30 01 01 # Page Switch to Page 1 W 30 00 01 # LDO output programmed as 1.8V and Level shifters powered up. W 30 02 00 # Page switch to Page 0 W 30 00 00 # Dac Instruction programming PRB #1 W 30 3c 01 # CODEC_CLKIN=MCLK.MCLK should be 12.288MHz W 30 04 00 # Codec Interface control Word length = 16bits.BCLK&WCLK inputs.I2S mode. W 30 1b 00 # Data slot offset 00 W 30 1c 00 # DAC NDAC Powered up, NDAC=1 W 30 0b 81 # DAC MDAC Powered up, MDAC=2 W 30 0c 82 # DAC OSR(9:0)-> DOSR=128 W 30 0d 00 # DAC OSR(9:0)-> DOSR=128 W 30 0e 80 # Only LDAC powered up.Dac path setup LDAC data Mono of LDAC and RDAC. RDAC data disabled.Soft step 1 per Fs. W 30 3f B0 # DAC volume for Left channel not muted.Right DAC muted. W 30 40 04 # LDAC digital gain 0dB W 30 41 00 # Page Switch to Page 1 W 30 00 01 # Master Reference Powered on W 30 01 10 # Output common mode for DAC set to 0.9V (default) W 30 0a 00 # LDAC AFIR is 6th order FIR filter and Powered up. W 30 03 00 # SPKL attn. Gain =0dB W 30 2E 00 # SPKL driver PGA Gain=6.0dB W 30 30 10 # SPK OSCP enabled , OCP Degltich=4, OTP enabled , OTP Deglitch=5 W 30 52 00 # SPK powered up W 30 2D 02

此致、

-Ivan Salazar

应用工程师