Other Parts Discussed in Thread: TLV320AIC34, REG101, REG102, REG103, REG104

主题中讨论的其他器件: REG101、 REG102、 REG103、 REG104

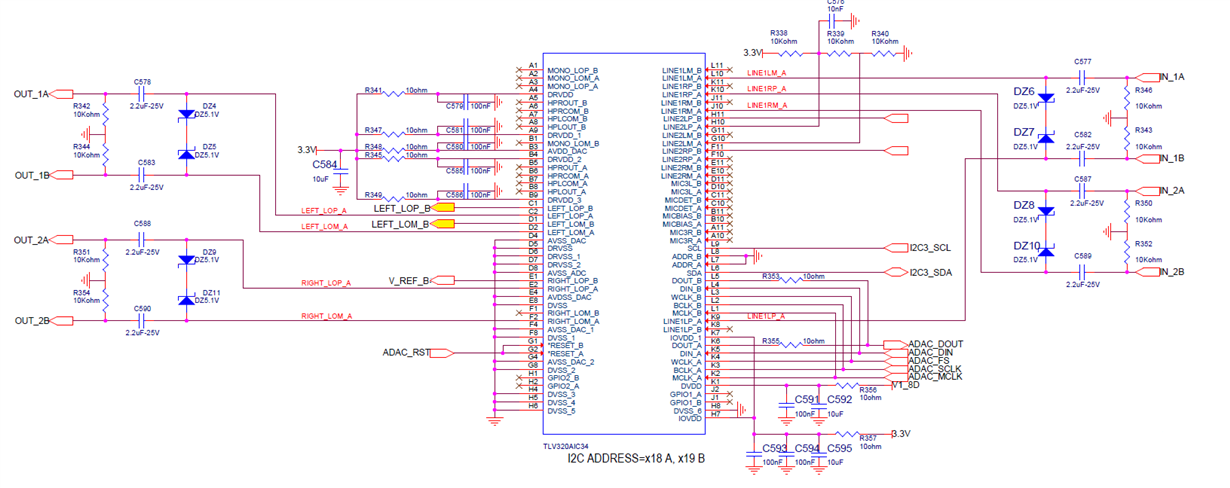

在我的电路板上、我有用于立体声音频接口(A 部分)和生成恒定极化信号(B 部分)、16KHz 采样率、DSP 接口的编解码器 TLV320AIC34。

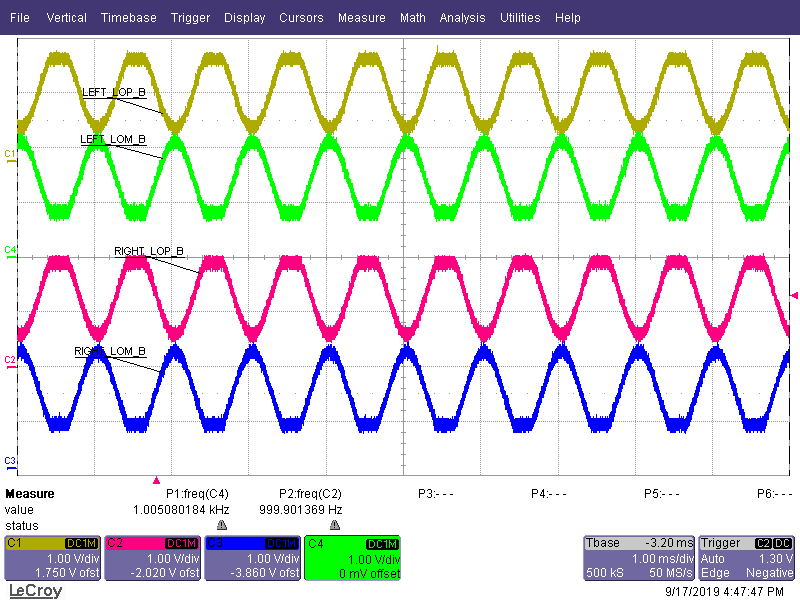

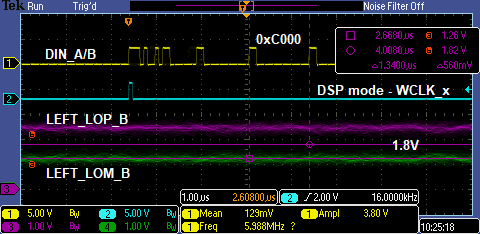

- 我注意到信号 LEFT_LOP_B/LEFT_LOM_B 的输出上出现了符号反转:当我在 DIN 接口上发送正值(16位:0x2000)时、我预计 LEFT_LOP_B 实际为 LEFT_LOM_B > LEFT_LOP_B、而当我写入负值(16位:0xe000)时则相反。 我有什么问题吗?

- 如果是单端输出、能否仅使用一个 RIGHT LOP_B 输出并将 LEFT_LOM_B 输出保持悬空?

- 在 DAC 部分中、我使用连接到 LEFT_LOP_A / LEFT_LOM_A 的 DAC_L3和连接到 Rright_LOP_A / Rright_LOM_A 的 DAC_R3 如何在 DAC 部分启用数字效果滤波器? 设置第1页上的系数还是第0页上有一些寄存器足够了?

谢谢

弗朗西斯科