https://e2e.ti.com/support/audio-group/audio/f/audio-forum/804836/pcm5242-no-output-in-hardware-mode

器件型号:PCM5242您好!

作为学习练习、我正在设计音频 DAC。 我将以模块化方式执行此操作、以便能够在不同的级上进行迭代、因此每个级都有用于连接到下一个板的接头。 我围绕 CP2615设计了第一阶段 、似乎可以正常工作。 现在、我正在研究 DAC (I2S ->模拟)、它是围绕 PCM5242芯片设计的。 该级将输出到最终级、即放大级。

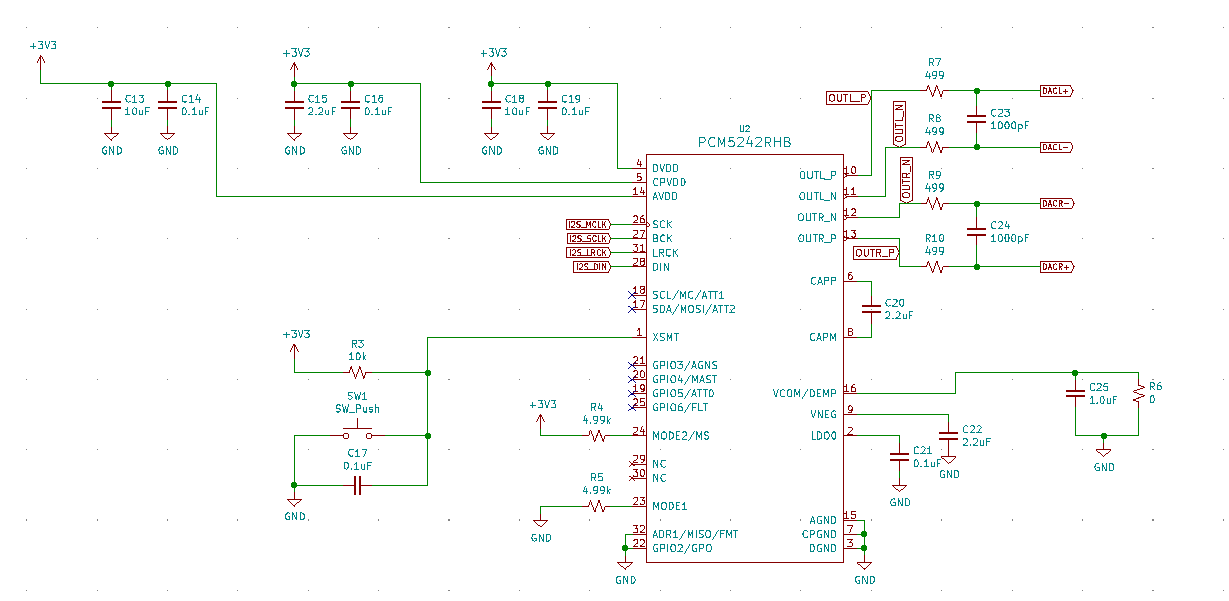

此处提供了相关的原理图部分、并进行了一些细微修改(见下文):

注释/更改:

- R4未组装、Mode2跳线至接地以设置硬件模式

- 未组装 R6

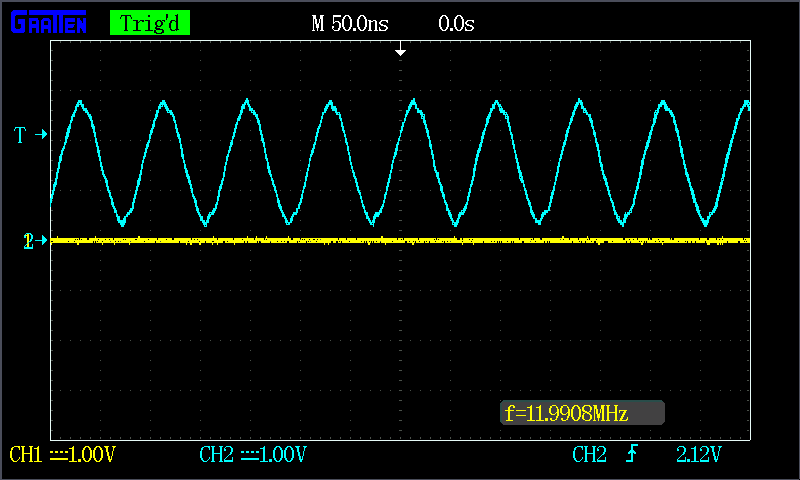

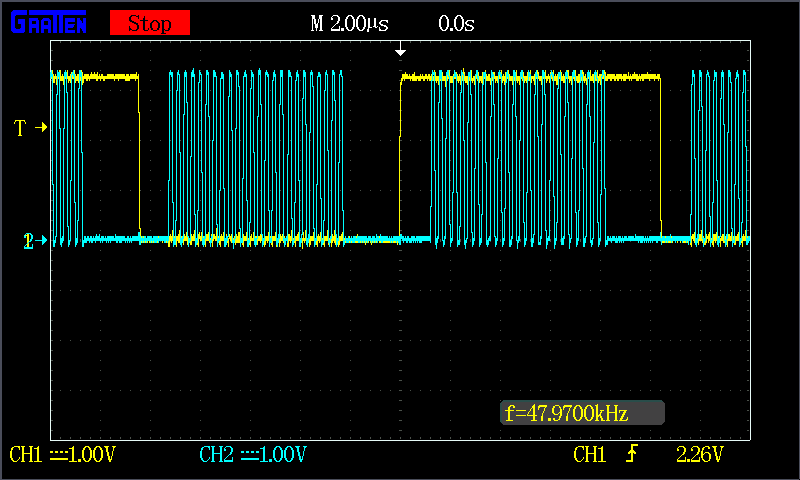

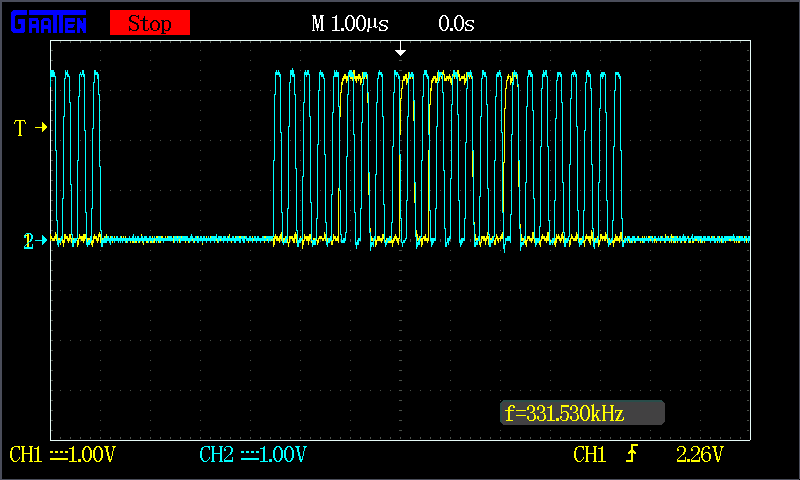

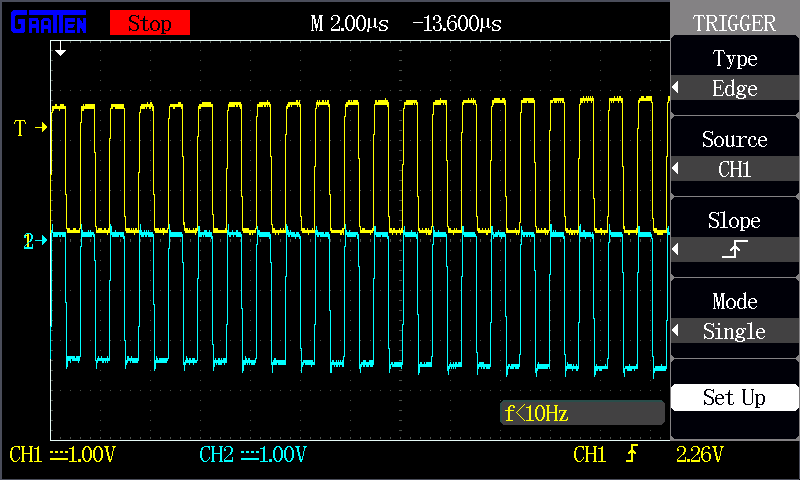

- I2S 输入信号@ 3.3V

- CAPP/CAPM 似乎工作正常

- VNEG 正在正确创建-3.3V

- LDO0正在正确创建1.8V

- 输入数据格式为24位 I2S

问题:没有任何输出引脚显示任何信号、我不确定要做什么来调试。 我用显微镜检查了所有的连接看起来都很好--我还能尝试什么,或者我在原理图上犯了错误,可能导致它无法正常工作?

谢谢、

Jonathan