Other Parts Discussed in Thread: PCM1864EVM, PCM1864

主题中讨论的其他器件: PCM1864

您好!

在主模式下使用 PCM1864EVM 时、您能告诉我建议的设置过程吗?

我想知道设置过程是否有任何限制、尤其是在更改 PLL 参数或分频比时。

此致、

加藤

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: PCM1864EVM, PCM1864

您好!

在主模式下使用 PCM1864EVM 时、您能告诉我建议的设置过程吗?

我想知道设置过程是否有任何限制、尤其是在更改 PLL 参数或分频比时。

此致、

加藤

您好 Kato、

Sanay 今天不在办公室、所以我会回应。

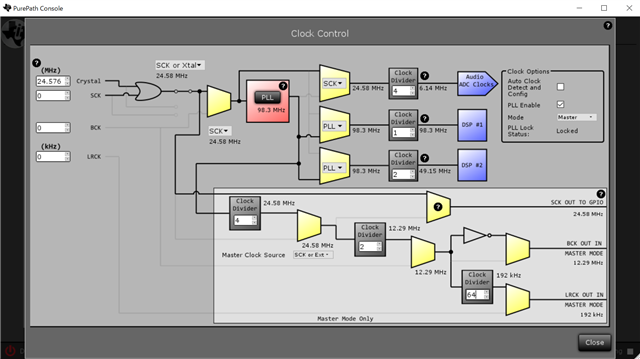

您是否有任何有关所需时钟速率的详细信息? 您可以使用 PPC2通过 GUI 界面配置计时、从而简化设置。 要使用主控模式、您需要一个外部主控时钟或晶体振荡器(EVM 应附带一个24.576MHz 板载晶体)。

有关详细信息、请参阅 EVM 用户指南: https://www.ti.com/lit/ug/slau615/slau615.pdf

通常、对于 常见时钟模式、无需手动设置 PLL 比率(例如24.576MHz MCLK、48kHz 采样率)

Brian

您好、Brian -San、

感谢您的回答。

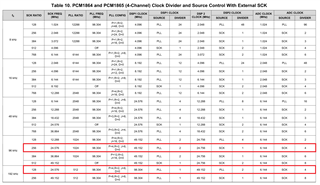

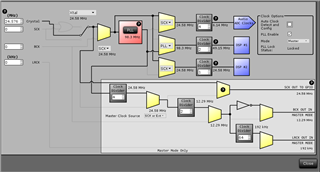

当在主模式下、在红色帧的每个设置条件下、当 CLKDET_EN ="1"时、PCM1864可与 GUI 正常配合使用。

接下来、如果 CLKDET_EN 从"1"设置为"0"、并且在更改 PLL 参数和分频比以将 fs 从96kHz 更改为192kHz 时、PCM1864将不会正常工作。 因此、当 CLKDET_EN 与 GUI 切换(自动时钟检测和配置)时、有时 PCM1864工作正常。

我正在考虑使用非音频时钟源运行 PCM1864、因此请向我提供您的建议。

此致、

加藤

您好、Brian -San、

有关主控模式中手动设置的问题、请参阅以下附加信息。

PLL 被解锁、所以不输出正确的时钟

-即使 PLL 被锁定,也不会输出正确的时钟

-即使 PLL 被锁定,也不会输出正确的数据

然后、PLL 参数和每个分频比通过 SCK_XI_SEL = 01 (所选 SCK)进行设置、PLL 通过更改为 SCK_XI_SEL = 10 (所选 XTAL)被正常锁定。

请给我评论吗?

此致、

加藤

您好、Sanjay-San、

感谢您的支持。

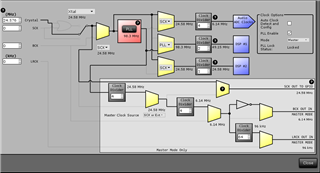

PCM1864EVM 的评估过程如下。

安装 J8和 J10的跳线、移除 J11的跳线

将 PCM1864EVM 连接到 PC、运行 GUI (PPC2)。

将 MODE0 (默认设置)更改为 MODE1以使用 GUI 更改主模式

设置 PLL 参数和分频比、使用"时钟控制"将 FS 从96kHz 更改为192kHz、如下所示

*不提供 SCLK、BCLK 和 LRCK、只提供 XTAL。

因此、PCM1864将无法正常工作。

那么、您能否使用 PCM1864EVM 重复此问题并建议如何改进此问题?

此致、

加藤

您好、Sanjay-San、

我已使用0x70的 PWRDN 确认您关于加电/断电序列的请求。

最终、PCM1864并不总是正常工作。 即使在主控模式下将采样率从96kHz 更改为192kHz、DOUT 也可能无法正确输出。 当然、在某些情况下会成功输出数据。

我不知道导致这种差异的原因、但在某些情况下、通过使用 GUI 切换"自动时钟检测和配置"来输出数据。

请使用 PCM1864EVM 重复此问题吗?

此致、

加藤

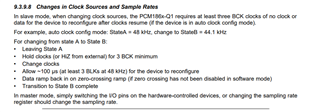

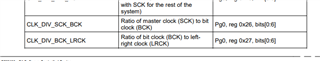

该系统具有一个自动时钟检测器、可在96kHz 和192kHz 频率下工作 。 如果我们在软件中设置 SCLK/LRCK 比率并启用自动时钟检测器、那么它可以设置正确的输出。 下表显示了自动检测选项。

CLKDET_EN Page.0 0x20) 默认为启用

CLK_DIV_SCK_bck (0x26)设置为0x00

对于 96k、CLK_DIV_BMCK_LRCK (0x27)设置为0xFF

对于192K、设置为0x7F

为了让自动时钟检测器重新配置系统,我们需要编写新的 I2C 设置,然后停止晶振输入。 一段时间后、我们需要启动晶体输入。 我不确定,但在 Crystal 终端上放置一个220欧姆的电阻器可能会停止晶振。

以便设置新配置

1.写入设置

2.在晶振终端上放置220欧姆的阻点来停止时钟

3.等待1秒钟

4.从晶振中移除220欧姆,启动时钟。

此致

Sanjay

我想为了实现这一点、我们需要提供新设置、然后停止时钟、然后再次重新启动时钟

您好、Kato-San、

Sanjay 和我在以下条件下测试了 EVM、结果如下:

拆下 J8和 J11、安装跳线 J10

接地 ADDR 引脚(MD5/AD)*J7,第二排

将 PCM1864EVM 连接到 PC、运行 GUI (PPC2)。

将 MODE0 (默认设置)更改为 MODE1以使用 GUI 更改主模式

设置 PLL 参数和分频比、使用"时钟控制"将 FS 从96kHz 更改为192kHz、如下所示

*不提供 SCLK、BCLK 和 LRCK、只提供 XTAL。

结果/观察结果:(模式1)

如果您有任何疑问、请告诉我