https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1176564/pcm1820-clock-jitter-immunity

部件号:PCM1820我们计划在接收数字音频输入的产品上使用 PCM1820、此时钟从此输入恢复。 恢复的时钟可能具有高达5.5ns 的抖动。 这会影响音频性能、还是集成的低抖动 PLL 会对此进行校正。 如果抖动过大、最大可接受量是多少?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1176564/pcm1820-clock-jitter-immunity

部件号:PCM1820我们计划在接收数字音频输入的产品上使用 PCM1820、此时钟从此输入恢复。 恢复的时钟可能具有高达5.5ns 的抖动。 这会影响音频性能、还是集成的低抖动 PLL 会对此进行校正。 如果抖动过大、最大可接受量是多少?

这是我建议在您的设置中尝试的内容。

您的 BCLK 是什么?

BCK /LRCK 比率通常是实时测量以配置内部时钟。

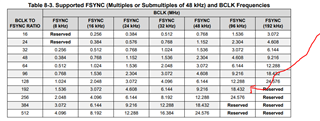

在 BCLK 为高电平的情况下(例如24.578MHz),增加5ns 的时间将导致时钟变为22Mhz。 自动电路正在寻找一个 BCLK/LRCK 比率来进行内部决策。 它看起来高于18MHz、因此可能不会做出错误的决策。

另一方面、允许的最高 BCLK 频率为25MHz、5ns 抖动会使其超过25MHz。

必须 在实际系统中检查抖动随 Tim 的变化及其对行为的影响。

我认为、如果您选择低 BCLK 频率、例如12.288Mhz 5ns 抖动、抖动将更好。

此时、这是我可以提供的最佳答案。