主题中讨论的其他器件:TAS6424、

您好,团队

当客户使用 TAS6424时、他们使用 TDM 信号。 将 MCLK 从12.288MHz 更改为24.576MHz 后、没有声音。

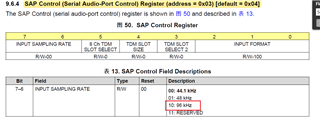

根据数据表、我认为 FSYNC、MCLK 和 SCLK 的比率不符合以下要求:

此时、除了将 SAP 寄存器中的 FSYNC 频率修改为96kHz、我们还需要做什么?

应如何配置256xF?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,团队

当客户使用 TAS6424时、他们使用 TDM 信号。 将 MCLK 从12.288MHz 更改为24.576MHz 后、没有声音。

根据数据表、我认为 FSYNC、MCLK 和 SCLK 的比率不符合以下要求:

此时、除了将 SAP 寄存器中的 FSYNC 频率修改为96kHz、我们还需要做什么?

应如何配置256xF?

尊敬的 Alan:

这是 TDM4还是 TDM8? 在 TDM 模式下、MCLK 和 SCLK 可连接在一起。 源必须为位宽、槽数和 FS 提供正确的比率。 如果 MCLK、SCLK、FSYNC 和 TDM (SDIN)设置正确、TAS6424将自动调整。 如果比率不正确、器件将无法正确解码。

如果您需要更多帮助、请发送有关数字时钟、插槽、位宽以及其他有用的信息。

此致、

Gregg Scott