Other Parts Discussed in Thread: PCM5100A

您好!

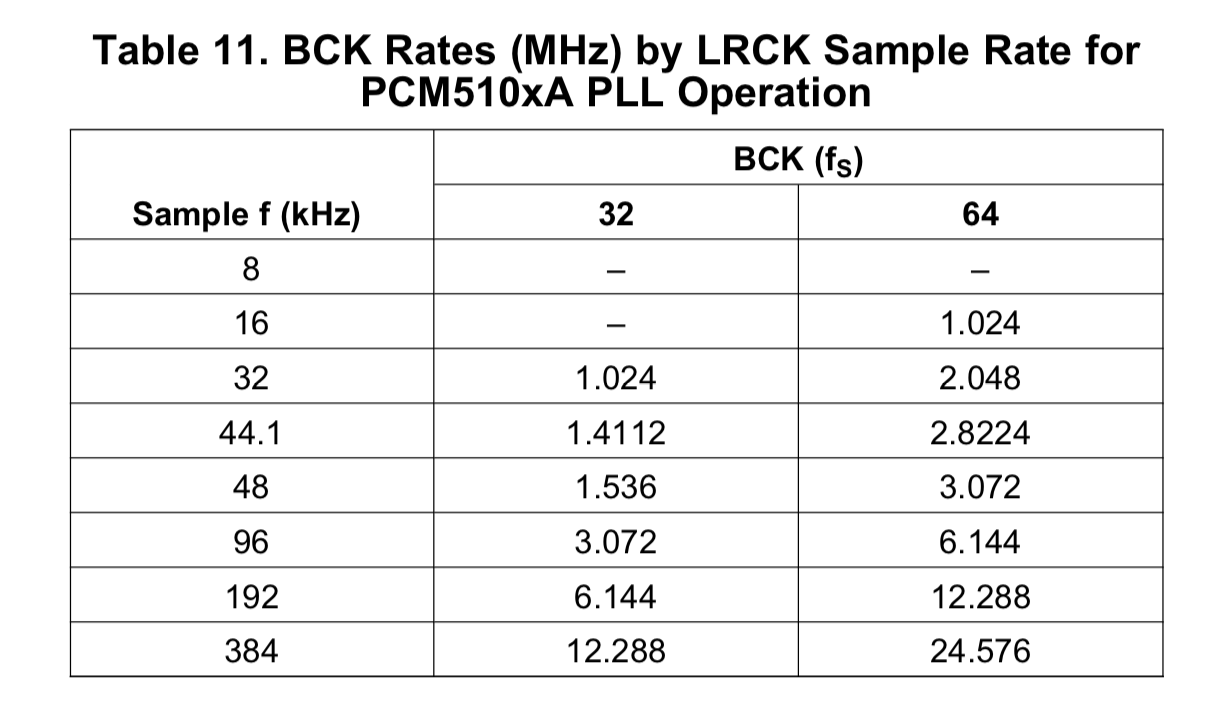

我们希望 在设计中使用 PCM5100A、但我们需要 DAC 通过简单的3线 I2S 接口(使用内部 PLL 从 BCLK 生成 SCLK)支持8kHz 采样率。 我们的 BCLK 以64*FS 运行、但我担心数据表中的表11:

这句话是否说明在8kHz 应用中无法使用 BCLK 来生成 SCLK? 如果是这样、我想知道它是否可以工作、但抖动性能会降低、还是根本不起作用? 如果是前者、我们可能会评估它是否可用于我们的应用。

提前感谢您的任何见解。

-Jay